1、2ポート・レジスタ・ファイル・メモリ・コンパイラ

コンパイラの概要

シルバコは、コンパイルされたメモリの設計において25年にわたる経験を有しています。その技術はシリコン・プルーブンで、何千ものデザイン、何百万ものウェハーで実績があります。

- SRAM(シングルおよびデュアル・ポート)、レジスタ・ファイル(1ポートおよび2ポート)、ROM向けコンパイラ

- 12のファウンドリおよびIDMにて導入

- 22nmまでのプロセスで使用可能

レジスタ・ファイル・コンパイラの特徴

- 低消費電力、汎用、高性能アプリケーションに最適化

- 複数の電源モードとオプションによる効率的な電源管理

- 複数のしきい値電圧(Vt)オプションと動作モードによる高性能化

- 高い歩留まり

- グローバルおよびローカルばらつきに強い設計について検証済み

- ECCビット、ワード・サイズ、アドレスの柔軟性により冗長性を確保

- 180nm、152nm、130nm、110nm、90nm、85nm、65nm、55nm、40nm、28nm、22nmの各テクノロジで利用可能

- 対象となるCMOSプロセスのバリエーションには、ファンドリが提供する高電圧、BCD、およびeFlashのCMOSプロセスのG、LP、SOI、およびSRAMが含まれます

- 他のノードやプロセスへのポーティングが容易

レジスタ・ファイル・メモリ・アーキテクチャ

- 高密度・低消費電力で設計された独自アーキテクチャにより、小面積化を実現

- スタンバイ、リテンション、シャットダウンなど、複数の低消費電力・モード

- 組み込み型スイッチに対応

- 以下に対応

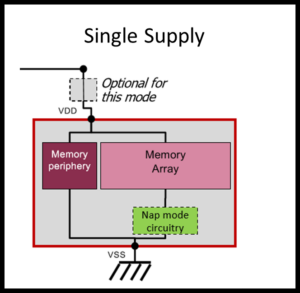

- 単一電源

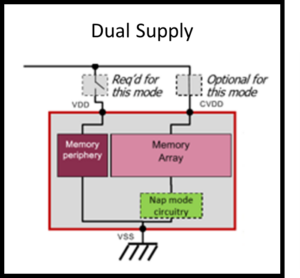

- ペリフェラルとコアに対して複数の電源レール

- データ保持モード

- 書き込み時のバイトモード

- BIST/R (Built in Self Test and Repair)オプションをサポート

| Feature | Benefit |

| High density | Industry leading area |

| Partitioned array | Extended battery life |

| Several operating modes | Up to 50% lower power consumption |

| Data retention mode | Reduce leakage current |

| BIST (optional) | Increase reliability and yield |

レジスタ・ファイル・ローパワー・動作モード

シルバコのレジスタ・ファイル・コンパイラは、リーク電流と起動時間が異なるさまざまな低消費電力動作モードがあります。

| Mode | Description | Leakage* |

| Active

Core: On @ Vdd |

· Read or write

· Core and Periphery powered and operational. · Dynamic power and small Leakage power consumption |

— |

| Standby

Core: On @ Vdd |

· No read or write.

· Core and Periphery powered but not operational · Small Leakage power but no Dynamic power consumption · Quick Wake Up time |

1.00 x |

| Retention

Core: On @ < Vdd |

· Periphery power turned off

· Core at minimum voltage to retain data · Lower Leakage power consumption than Nap · Slow Wake Up time depends on powering up periphery switches and other circuits |

0.54 x |

| Shutdown (Data Content Lost)

Core: OFF |

· Core and Periphery switched off

· Lowest Leakage power consumption · Slowest Wake Up time |

— |

メモリ・コンフィギュレーション

シルバコのレジスタ・ファイル・コンパイラは、さまざまな電源コンフィギュレーションをサポートしています。 また、広範囲なマルチプレクサとワード幅のコンフィギュレーションをサポートしています。