Jivaro寄生リダクションによる回路シミュレーションの加速

Jivaroを簡単に紹介した後、シミュレーション・フローを向上する手法を示し、高度なネットリスト・リダクションを行うために必要な機能および制御を確認します。

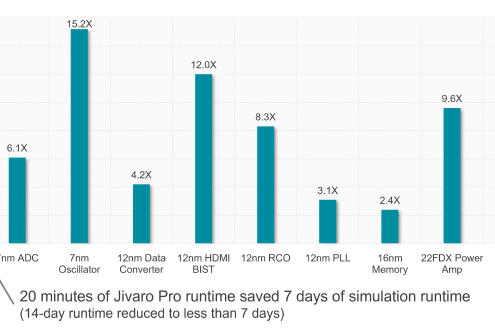

寄生素子リダクション

Jivaro Proは、寄生素子ネットワークの削減によるシミュレーション時間の短縮に特化した独自のスタンドアローンソリューションです。Jivaro Proの高いリダクション率は、シミュレーション時間を数日から数時間にまで劇的に短縮することが証明されています。

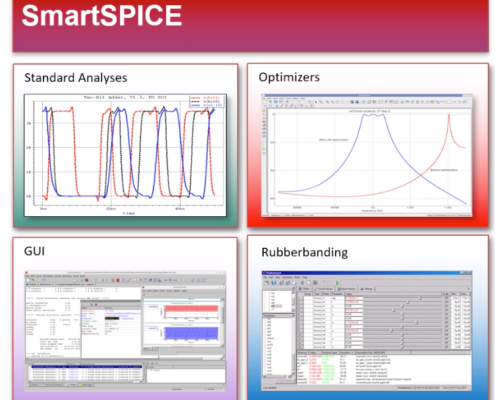

回路ラバーバンド

SmartSpiceとGatewayのラバーバンド機能を使えば、アナログ設計の改善が容易になります。モデルやデバイスのインスタンス・パラメータの値を任意の組み合わせで変更すると、ラバーバンド機能によって回路性能の変化がリアルタイムにフィードバックされます。

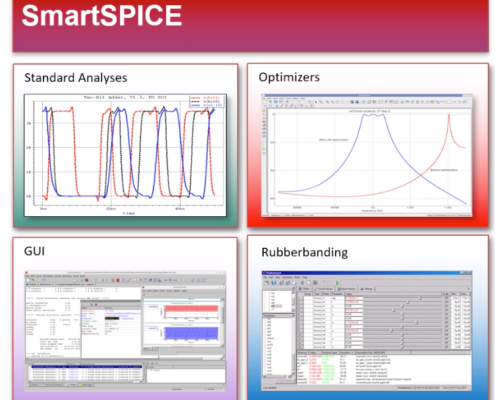

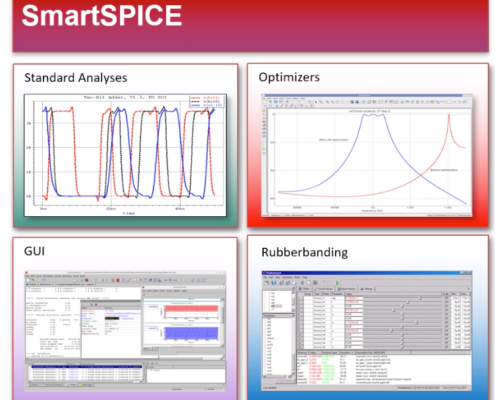

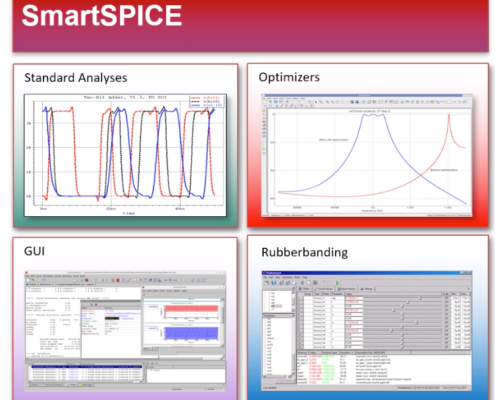

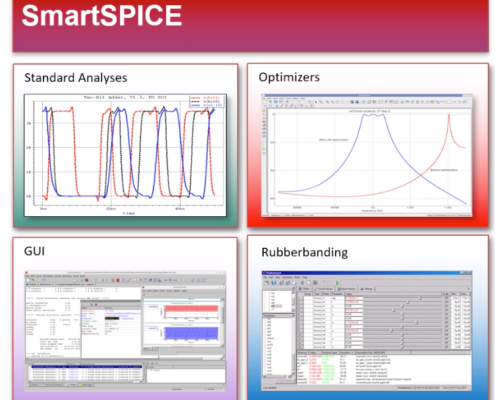

回路シミュレータ

シルバコのSmartSpice™は、業界をリードする精度を誇る高性能パラレルSPICEシミュレータです。複雑な高精度アナログおよびミックスドシグナル回路のシミュレーション、メモリ、カスタム・デジタル設計、先端半導体プロセスのセル・ライブラリの特性評価などのアプリケーションに対応する、実績のある包括的なソリューションです。

アナログ・シミュレーション

シルバコのSmartSpiceは、業界をリードする精度を実現する高性能なパラレルSPICEシミュレータです。複雑な高精度アナログ/ミックスドシグナル回路のシミュレーション、メモリ、カスタム・デジタル設計、先端半導体プロセスのセル・ライブラリの特性評価などのアプリケーションに対応した、実績のある包括的なソリューションです。複数のソルバー、ステッピング・アルゴリズム、計算技術を導入したインテリジェントなアーキテクチャを採用しています。

シルバコ、HDL Design HouseとアナログおよびデジタルICデザイン・サービスで提携

米国カリフォルニア州サンタクララ発 – 2019年9月16日 - HDL Design HouseとSilvaco, Inc. (以下、シルバコ) は、本日、アナログ/デジタルICデザイン・サービス、そしてフルターンキー・ソリューションを世界中の半導体ファブレス企業に提供するべく協業することを発表しました。

Verilog-Aを使用したロバストなSPICEモデリング: 原則と実践テクニック

本ウェビナーは、Verilog-Aを使用したSPICEコンパクトモデルのロバストなコーディングについて、専門的なガイダンスを行うことを目的とします。

SmartSpice解析エンジンの設計フローへの適用

本ウェビナーでは、さまざまなフローの構成要素を詳しく理解できるよう説明し、運用を可能にする、あるいは妨げる要因とパフォーマンスを最適化する方法について説明します。

トランジスタ・レベル・シミュレーションの理解および最適化

本ウェビナーでは、並列およびFastSPICE解析モードを含め、SmartSpiceシミュレータの核心部をさらに詳しく説明します。

TCADとSPICEを駆使した太陽電池モデリング

このウェビナーでは、太陽電池とソーラーパネルのTCADからSPICEに至るシミュレーション・フローを概観し、またその関連の手法について紹介します。