Victory Process에서 CMOS 기술에 대한 모델링 프레임워크 이해

최신 세대의 CMOS 소자 공정은 단순한 확산 모델로 정밀하게 시뮬레이션할 수 없습니다. 이는 기술 노드의 크기가 지속적으로 감소하기 때문이며, 이는 접합부는 더 얕고 도핑된 부분은 더 작다는 것을 의미합니다. 또한, 일시적인 확산 메커니즘이 이러한 부분의 공정과 최종 소자 특성에 대해 점점 더 큰 역할을 한다는 것을 나타냅니다. 특히, 비평형 결함과 확산 메커니즘에 미치는 영향을 다양한 도핑 물질의 공동 상호작용과 함께 모델링해야 합니다.

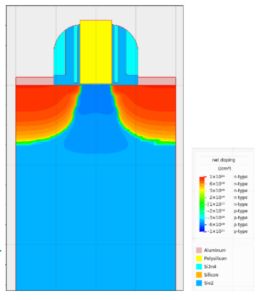

이번 시간에 Victory Process에서 이러한 메커니즘을 시뮬레이션하는 방법과 모델을 사용하여 공정 시뮬레이션을 설정하는 방법을 소개합니다. 그 다음, 평면 CMOS 예제를 통해 이러한 모델을 활용하여 결과가 어떻게 개선되는지 살펴봅니다.

내용

- CMOS 확산 모델 물리학

- CMOS 확산 모델 특징

- 데크에서 CMOS 확산 모델을 사용하는 방법

- CMOS 모델의 실제 응용 사례

발표

Thomas Grenouilloux 박사

Thomas Grenouilloux 박사

참석 대상

공정 엔지니어, 시뮬레이션 엔지니어, 제조 엔지니어, 제품 관리자, 엔지니어링 관리자