최신 로직의 신속한 구축: 공정 및 소자 시뮬레이션, 보정, FTCO™ 워크플로우

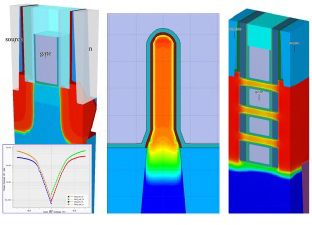

무어의 법칙에 따라 반도체 기술이 지속적으로 발전하면서, 트랜지스터 아키텍처는 3차원 시대에 진입하였습니다. FinFET은 첨단 로직 노드의 지배적인 위치에 있으며, 공정 미세화에 따라 게이트 올 어라운드(GAA) 나노시트 트랜지스터가 지속적인 정전 제어 및 성능을 위해 중요한 방안으로 떠오르고 있습니다. 이번 시간에 최신 노드 FinFET 소자의 모델링 및 시뮬레이션에 실용적인 워크플로우를 소개하고, 아키텍처가 진화함에 따라 동일한 방법론이 어떻게 확장되는지 나타내기 위해 GAA 나노시트를 설명합니다.

무어의 법칙에 따라 반도체 기술이 지속적으로 발전하면서, 트랜지스터 아키텍처는 3차원 시대에 진입하였습니다. FinFET은 첨단 로직 노드의 지배적인 위치에 있으며, 공정 미세화에 따라 게이트 올 어라운드(GAA) 나노시트 트랜지스터가 지속적인 정전 제어 및 성능을 위해 중요한 방안으로 떠오르고 있습니다. 이번 시간에 최신 노드 FinFET 소자의 모델링 및 시뮬레이션에 실용적인 워크플로우를 소개하고, 아키텍처가 진화함에 따라 동일한 방법론이 어떻게 확장되는지 나타내기 위해 GAA 나노시트를 설명합니다.

실바코의 Victory TCAD를 활용하여 소자 시뮬레이션 플로우를 보정하는 과정에서, 양자 구속, 밴드 구조 보정, 변형 엔지니어링, 이동도 거동 등, 소자를 정확하게 설명하는데 필요한 주요 물리적 효과 및 모델링 고려 사항을 집중적으로 살펴봅니다. Victory Device를 기반으로 시뮬레이션 보정 및 참조 데이터 검증 방안을 설명합니다. 마지막으로, Victory Analytics와 Fab Technology Co-Optimization (FTCO™)에서 다차원적으로 공정/설계를 탐색하여, 개발 주기를 단축하고, 차세대 고성능, 저전력 로직를 위해 디자인 윈도우를 최적화하는 방법을 소개합니다.

다음 사항을 살펴봅니다.

- FinFET 및 나노시트/GAA: 최신 노드에서의 변경 사항

- 최신 로직 시뮬레이션에 실용적인 Victory TCAD 워크플로우

- TCAD 루프에서 교정/검증 적용

- FTCO™에서 다중 파라미터 탐색 및 최적화

- DoE + 분석을 사용하여 민감도와 절충점을 빠르게 탐색

- FTCO에서 대화형 디지털 트윈 구축

발표

Jay Zhou

Jay Zhou

실바코 수석 TCAD FAE

Jay Zhou는 반도체 업계에서 9년간 경력을 쌓은 TCAD FAE입니다. 실바코에 입사하기 전에 주요 반도체 파운드리에서 공정 개발과 소자 최적화를 담당하였습니다. 현재 TCAD 고객을 위한 기술 지원 및 애플리케이션 솔루션을 제공하고 있습니다.

참석 대상

공정 엔지니어, 시뮬레이션 엔지니어, 제조 엔지니어, 제품 관리자, 엔지니어링 관리자.

일시 (한국 시각)

3/26 11:00 am (10:00 Beijing)

3/26 7:00 pm (11:00 Paris)

3/27 2:00 am (10:00 Santa Clara)