Shallow-Trench-Isolation (STI) Effects in BSIM4 and HiSIM MOSFET Models in SmartSpice & UTMOST-III

Introduction

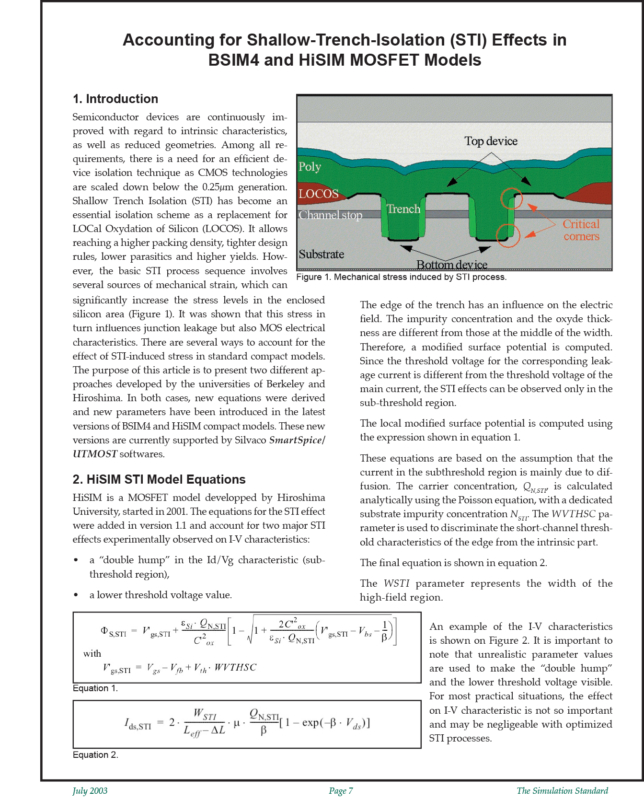

Semiconductor devices are continuously improved with regard to intrinsic characteristics, as well as reduced geometries. Among all requirements, there is a need for an efficient device isolation technique as CMOS technologies are scaled down below the 0.25µm generation. Shallow Trench Isolation (STI) has become an essential isolation scheme as a replacement for LOCal Oxydation of Silicon (LOCOS). It allows reaching a higher packing density, tighter design rules, lower parasitics and higher yields. However, the basic STI process sequence involves several sources of mechanical strain, which can significantly increase the stress levels in the enclosed silicon area (Figure 1). It was shown that this stress in turn influences junction leakage but also MOS electrical characteristics. There are several ways to account for the effect of STI-induced stress in standard compact models. The purpose of this article is to present two different approaches developed by the universities of Berkeley and Hiroshima. In both cases, new equations were derived and new parameters have been introduced in the latest versions of BSIM4 and HiSIM compact models. These new versions are currently supported by Silvaco SmartSpice/UTMOST softwares.