Interconnect Parasitic Extraction of BiCMOS Cell Using Silvaco CLEVER

1. Introduction

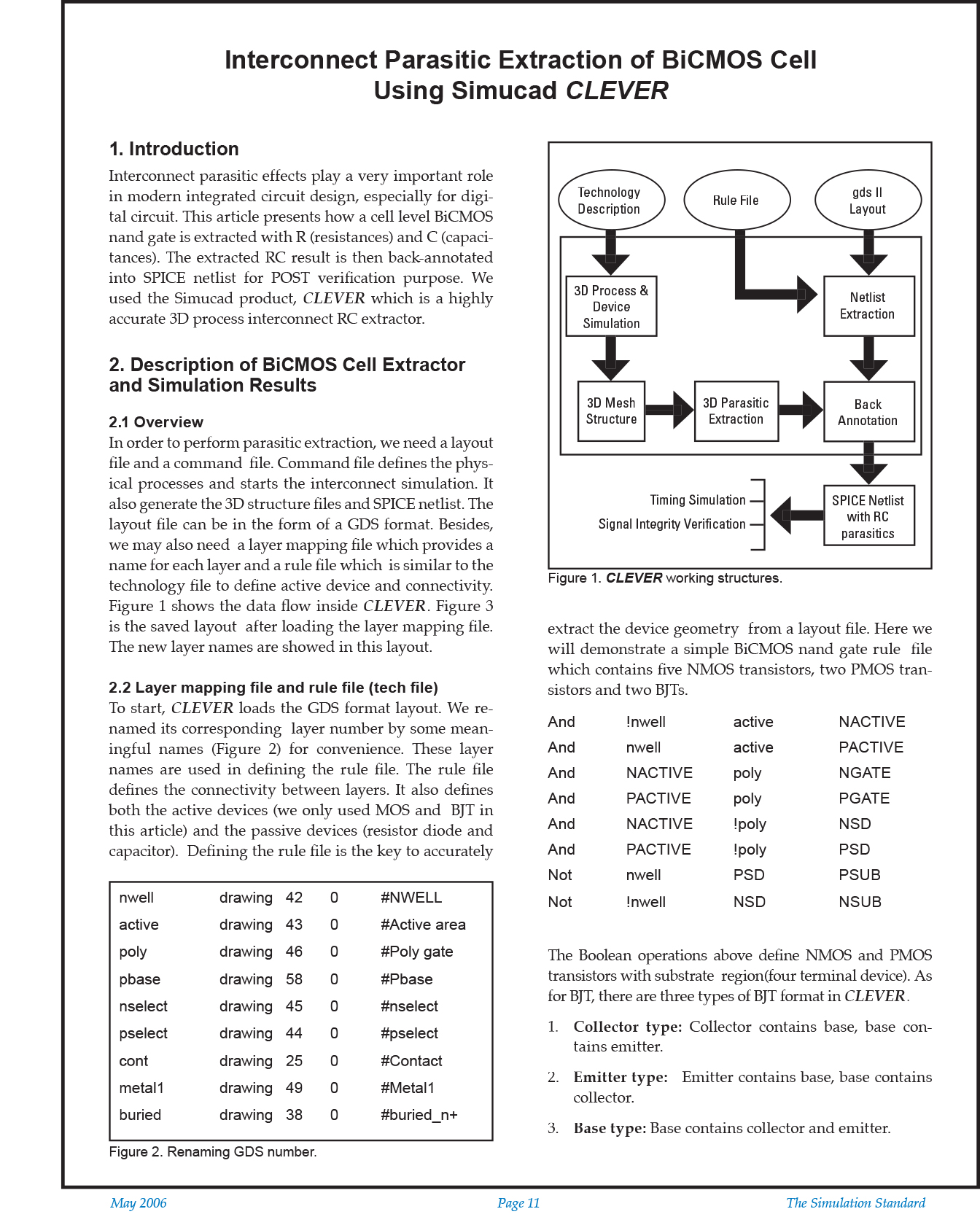

Interconnect parasitic effects play a very important role in modern integrated circuit design, especially for digital circuit. This article presents how a cell level BiCMOS nand gate is extracted with R (resistances) and C (capacitances). The extracted RC result is then back-annotated into SPICE netlist for POST verification purpose. We used the Silvaco product, CLEVER which is a highly accurate 3D process interconnect RC extractor.

2. Description of BiCMOS Cell Extractor and Simulation Results

2.1 Overview

In order to perform parasitic extraction, we need a layout file and a command file. Command file defines the physical processes and starts the interconnect simulation. It also generate the 3D structure files and SPICE netlist. The layout file can be in the form of a GDS format. Besides, we may also need a layer mapping file which provides a name for each layer and a rule file which is similar to the technology file to define active device and connectivity. Figure 1 shows the data flow inside CLEVER. Figure 3 is the saved layout after loading the layer mapping file. The new layer names are showed in this layout.