Interconnect Parasitic Accuracy & Speed Improvements in New Clever Release

Introduction

This article introduces the new features and numerical schema implemented in the most recent release of Clever from Silvaco. In this new release, both memory handling and simulation time are optimized to allow the input of larger simulation structures. In addition, the release offers greater control over the accuracy benchmarks necessary for extracted parasitic elements.

Parasitic Extraction Accuracy

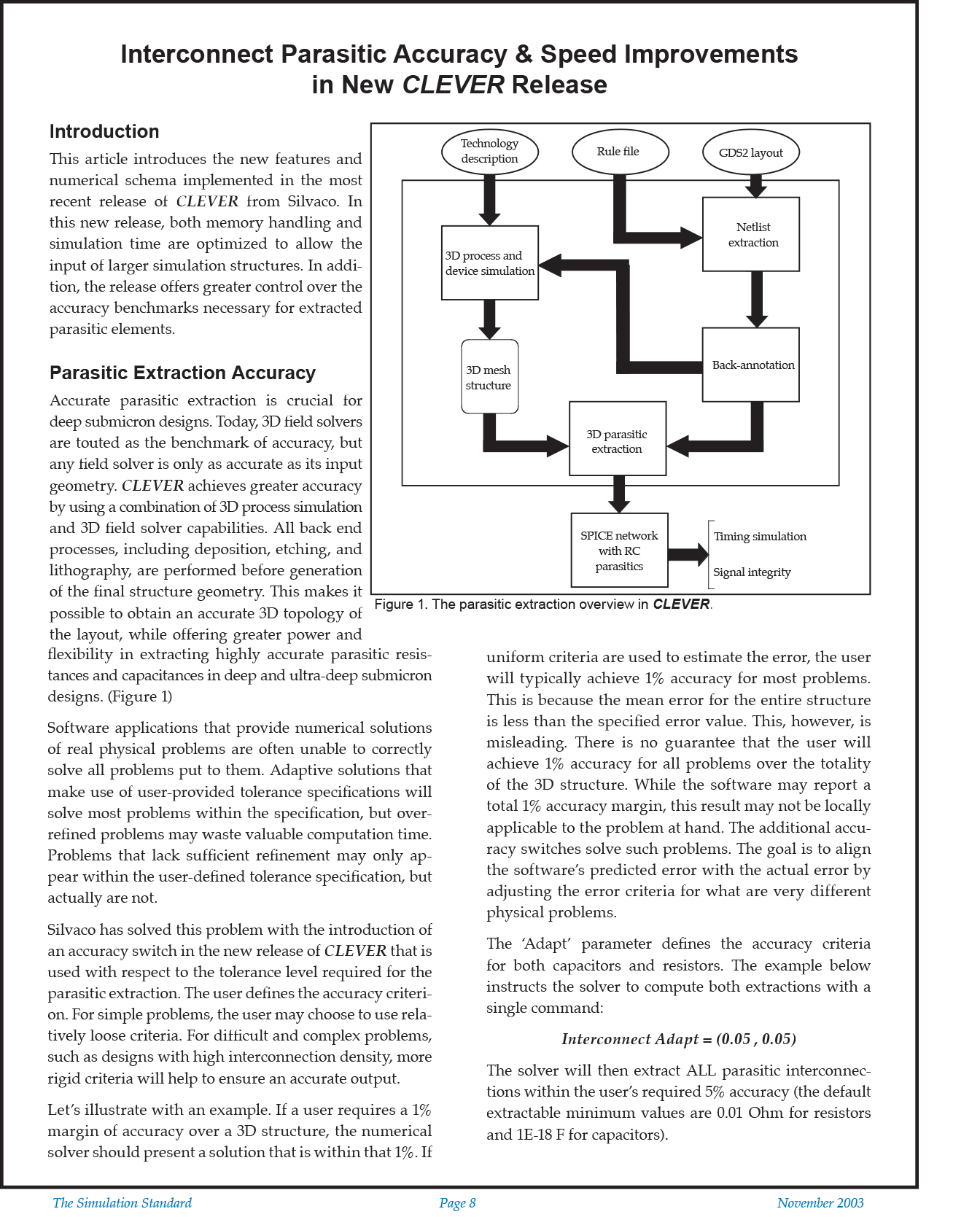

Accurate parasitic extraction is crucial for deep submicron designs. Today, 3D field solvers are touted as the benchmark of accuracy, but any field solver is only as accurate as its input geometry. Clever achieves greater accuracy by using a combination of 3D process simulation and 3D field solver capabilities. All back end processes, including deposition, etching, and lithography, are performed before generation of the final structure geometry. This makes it possible to obtain an accurate 3D topology of the layout, while offering greater power and flexibility in extracting highly accurate parasitic resistances and capacitances in deep and ultra-deep submicron designs. (Figure 1)