Behavioral Modeling of PLL Using Verilog-A with SmartSpice

Introduction

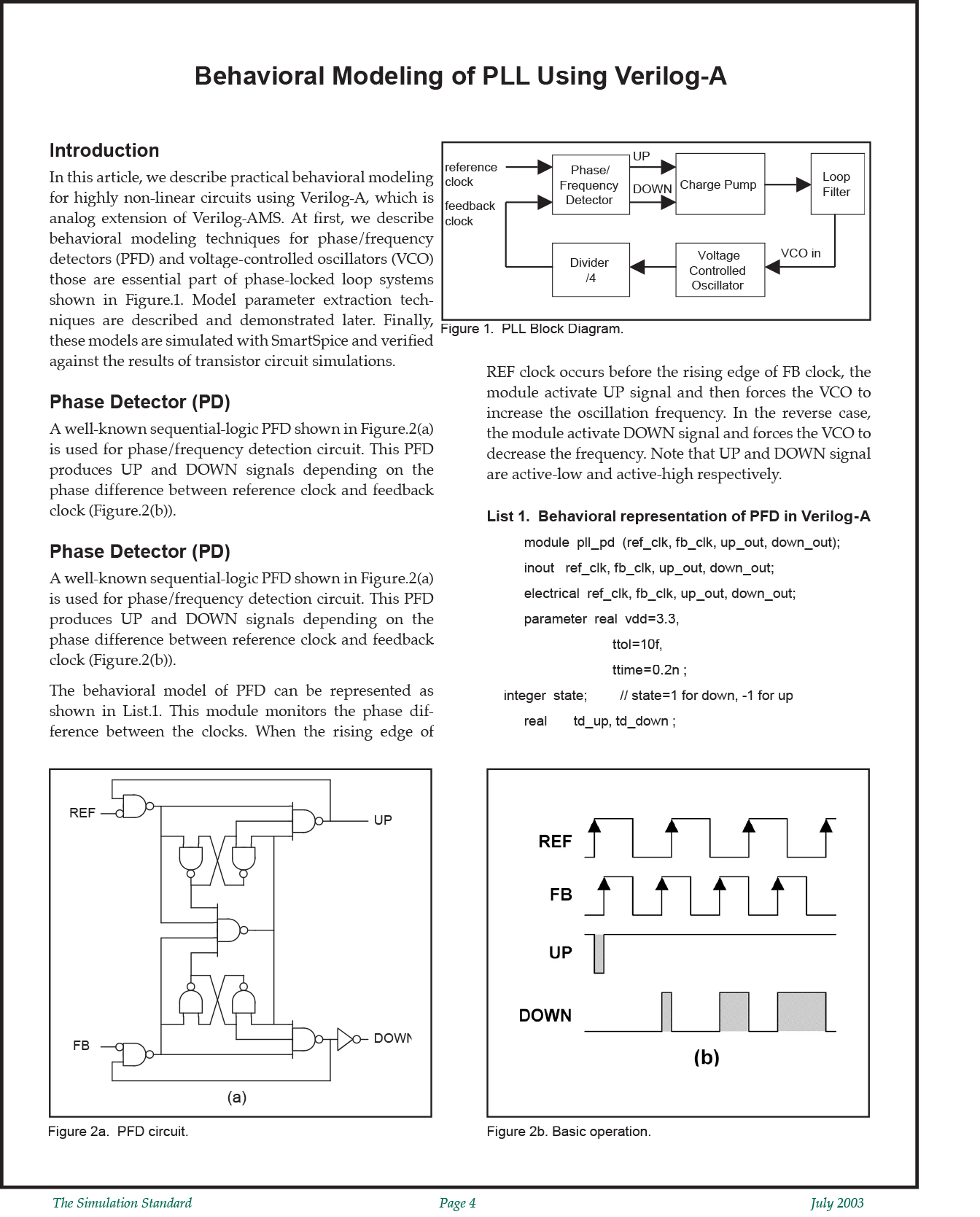

In this article, we describe practical behavioral modeling for highly non-linear circuits using Verilog-A, which is analog extension of Verilog-AMS. At first, we describe behavioral modeling techniques for phase/frequency detectors (PFD) and voltage-controlled oscillators (VCO) those are essential part of phase-locked loop systems shown in Figure.1. Model parameter extraction techniques are described and demonstrated later. Finally, these models are simulated with SmartSpice and verified against the results of transistor circuit simulations.