Build Better Pixels Faster: TCAD-Powered Digital Twins for Next-Gen CIS

Accelerating CMOS Image Sensor (CIS) innovation requires far more than traditional process and device exploration. As pixel architectures become increasingly complex—driven by demands for higher sensitivity, reduced noise, improved color fidelity, and aggressive scaling—engineers need faster, more predictive ways to design and optimize next-generation pixels.

Accelerating CMOS Image Sensor (CIS) innovation requires far more than traditional process and device exploration. As pixel architectures become increasingly complex—driven by demands for higher sensitivity, reduced noise, improved color fidelity, and aggressive scaling—engineers need faster, more predictive ways to design and optimize next-generation pixels.

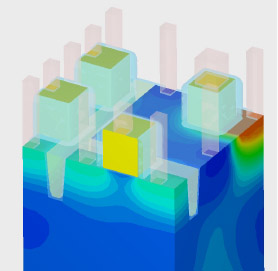

In this webinar, we show how TCAD-powered digital twins enable teams to build better pixels faster by providing deep, physics-based insight into the electro-optical mechanisms that define CIS performance. Using Silvaco’s Victory TCAD™ and the FTCO™ flow, attendees will learn how multi-physics simulation, calibrated models, virtual experimentation, and advanced analytics dramatically shorten development cycles while improving accuracy and yield.

We begin with a concise overview of CIS device fundamentals and pixel architecture trends, then demonstrate how predictive TCAD digital twins can reveal latent variables, identify design trade-offs, and accelerate process–device–optical co-optimization. Practical examples will highlight how Victory TCAD, Victory DoE, and Victory Analytics create a high-fidelity virtual environment for exploring new pixel concepts, improving performance, and reducing costly prototyping iterations.

Whether developing advanced imaging systems or enhancing existing CIS technologies, this webinar will show how simulation-driven digital twins empower engineers to innovate faster, reduce risk, and deliver competitive, high-performance pixels to market.

What You Will Learn

- CIS fundamentals (Structure and operation)

- Sub-micron CIS process and design tradeoffs

- Factors impacting CIS performance and their interplay

- Role of TCAD in CIS design, development, and optimization

- AI/ML-assisted pixel co-design

- CIS future directions

Presenter

Hamid Soleimani, FAE Manager USA & EMEA

Hamid Soleimani, FAE Manager USA & EMEA

Received B.S. and M.S. degrees from LSU, Baton Rouge, La. He joined Silvaco in 2023 as a TCAD FAE manager. He has extensive experience in TCAD simulation, device design, process integration, and reliability engineering of advanced CMOS logic, CMOS image sensor, and power devices. He is the author or coauthor of several publications and patents.

WHO SHOULD ATTEND:

Device engineers, process engineers, simulation engineers, fabrication engineers, product engineers, product managers, and engineering management.