Simulation Standard

Silvaco面向半导体工艺和器件仿真工程师推出的技术刊物

Transient Simulations of Edge Emitting Fabry-Perot InP/InGaAsP Laser Diode Using Silvaco TCAD Tools

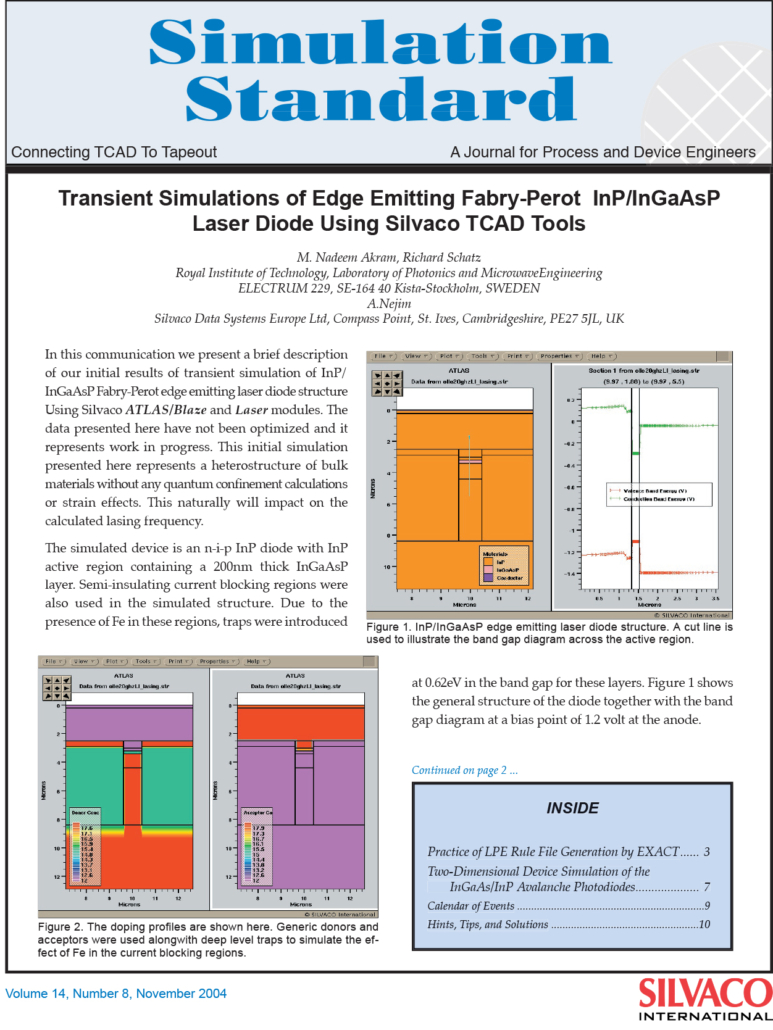

In this communication we present a brief description of our initial results of transient simulation of InP/InGaAsP Fabry-Perot edge emitting laser diode structure Using Silvaco ATLAS/Blaze and Laser modules. The data presented here have not been optimized and it represents work in progress. This initial simulation presented here represents a heterostructure of bulk materials without any quantum confinement calculations or strain effects. This naturally will impact on the calculated lasing frequency.

Practice of LPE Rule File Generation by Exact

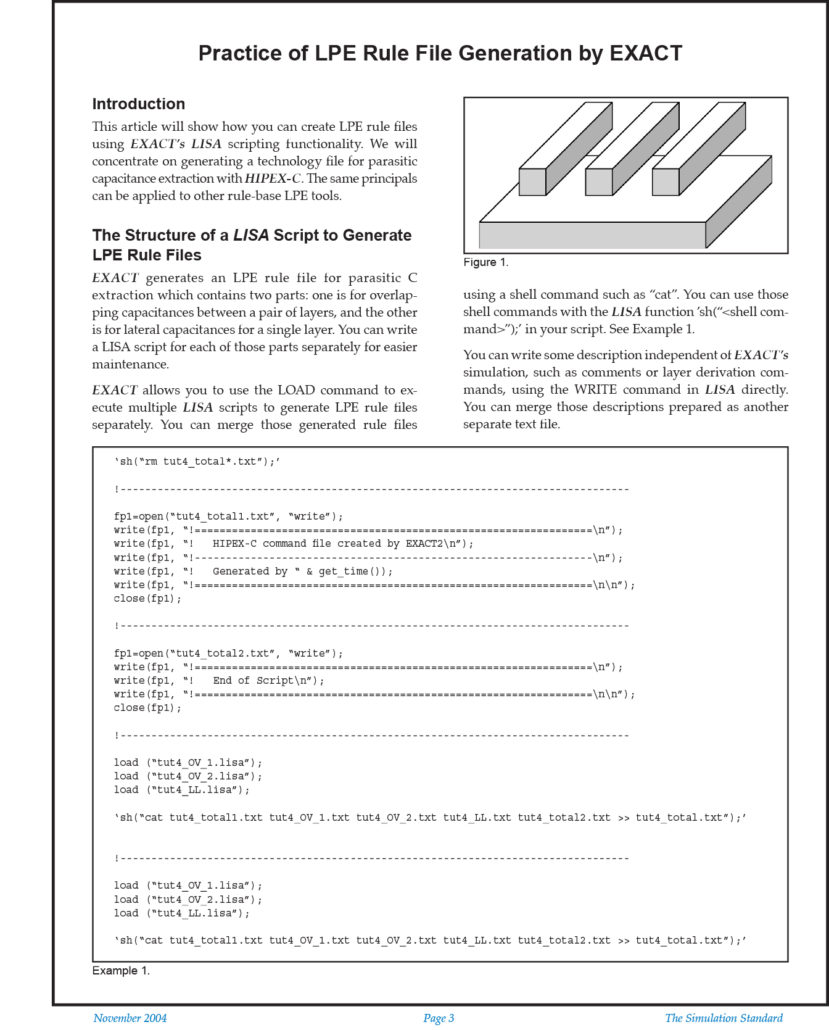

This article will show how you can create LPE rule files using EXACT’s LISA scripting functionality. We will concentrate on generating a technology file for parasitic capacitance extraction with HIPEX-C. The same principals can be applied to other rule-base LPE tools.

Two-Dimensional Device Simulation of the InGaAs/InP Avalanche Photodiodes

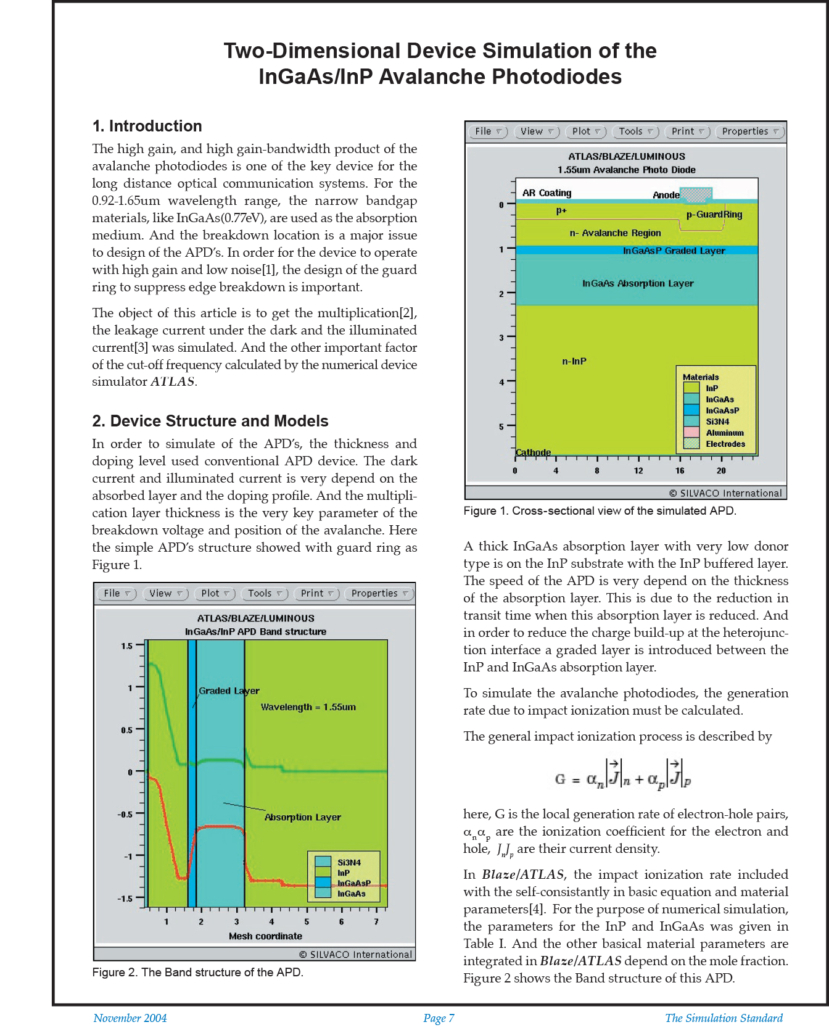

The high gain, and high gain-bandwidth product of the avalanche photodiodes is one of the key device for the long distance optical communication systems. For the 0.92-1.65um wavelength range, the narrow bandgap materials, like InGaAs(0.77eV), are used as the absorption medium. And the breakdown location is a major issue to design of the APD’s. In order for the device to operate with high gain and low noise[1], the design of the guard ring to suppress edge breakdown is important.

Resistor and Capacitor L/W Parameters in LVS Comparison

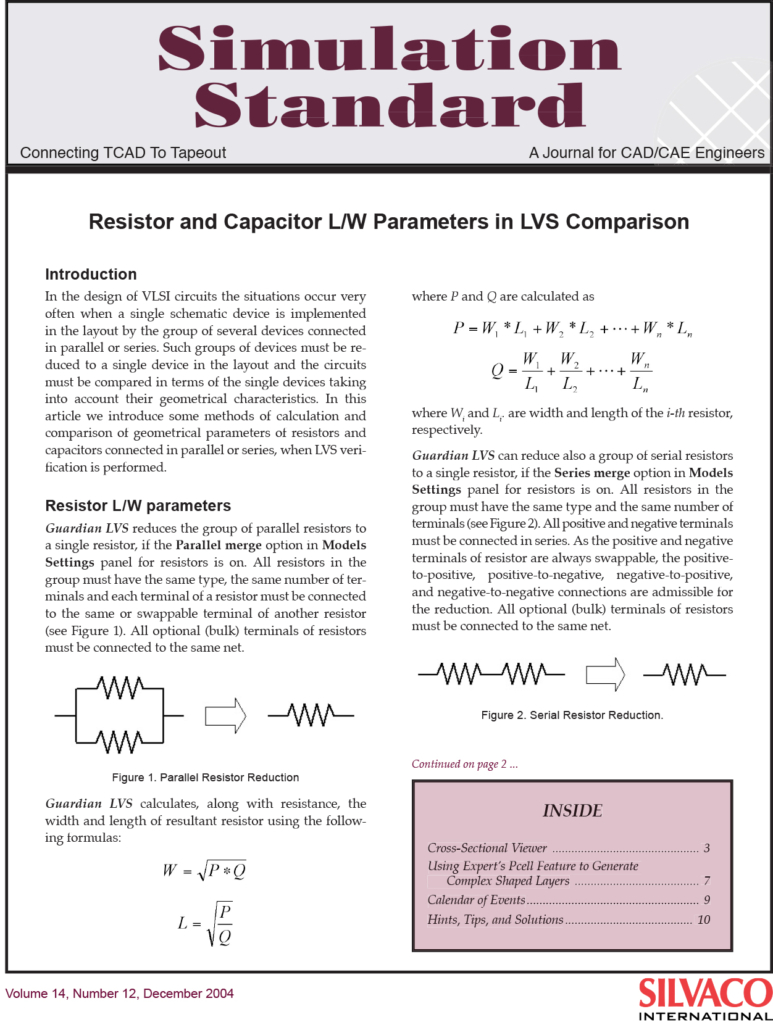

In the design of VLSI circuits the situations occur very often when a single schematic device is implemented in the layout by the group of several devices connected in parallel or series. Such groups of devices must be reduced to a single device in the layout and the circuits must be compared in terms of the single devices taking into account their geometrical characteristics. In this article we introduce some methods of calculation and comparison of geometrical parameters of resistors and capacitors connected in parallel or series, when LVS verification is performed.

Fast and Accurate Simulation of the Steady-State of Voltage Controlled Oscillators with SmartSpice-RF

A novel simulation method of the steady-state of oscillators, based on Harmonic Balance (HB), is presented. A comparison with regular transient simulations demonstrates its advantages on a feedback voltage-controlled oscillator (VCO).

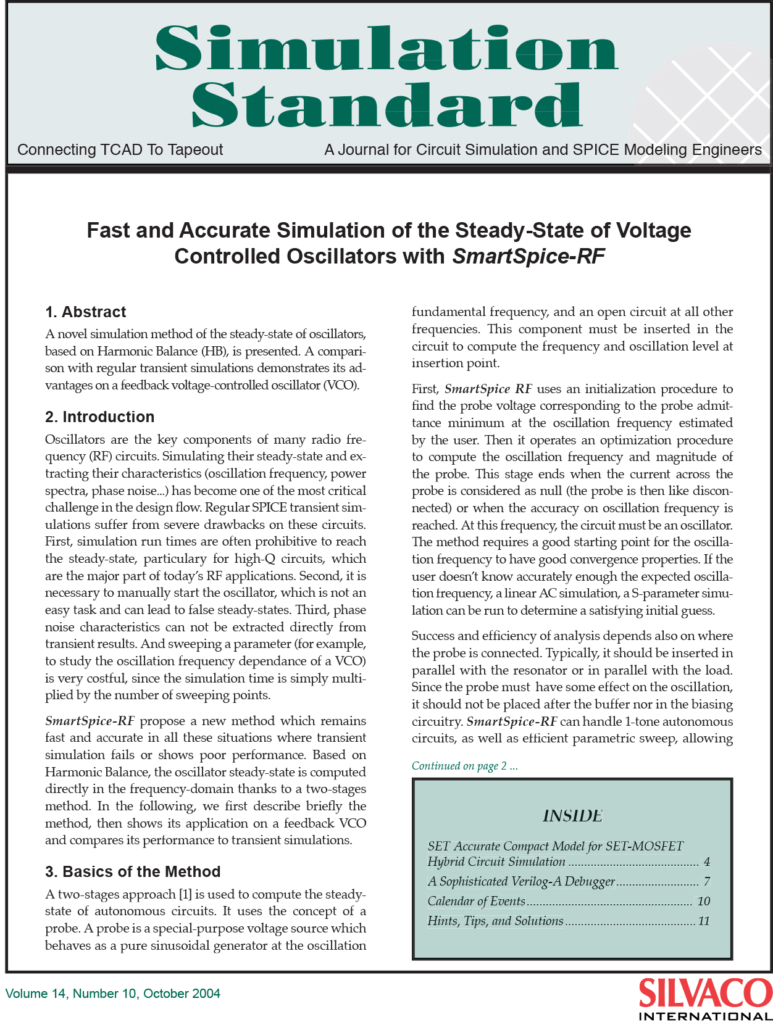

A Sophisticated Verilog-A Debugger

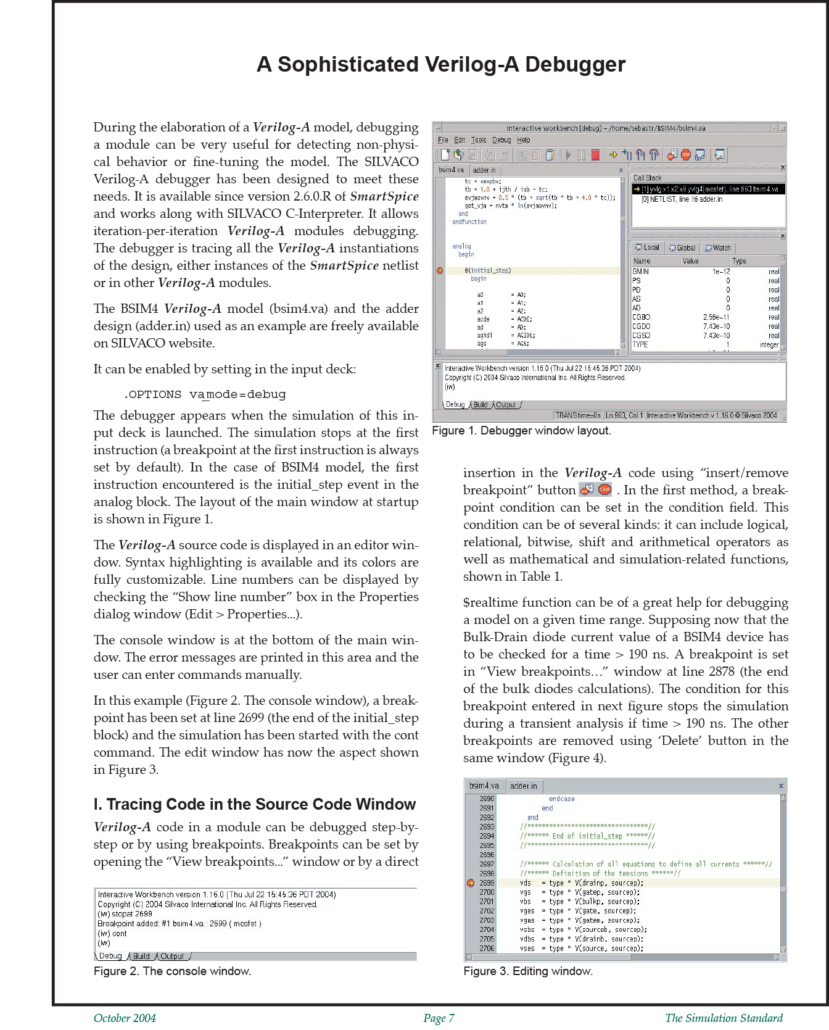

During the elaboration of a Verilog-A model, debugging a module can be very useful for detecting non-physical behavior or fine-tuning the model. The SILVACO Verilog-A debugger has been designed to meet these needs. It is available since version 2.6.0.R of SmartSpice and works along with SILVACO C-Interpreter. It allows iteration-per-iteration Verilog-A modules debugging. The debugger is tracing all the Verilog-A instantiations of the design, either instances of the SmartSpice netlist or in other Verilog-A modules.