Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

Behavioral Modeling of PLL Using Verilog-A with SmartSpice

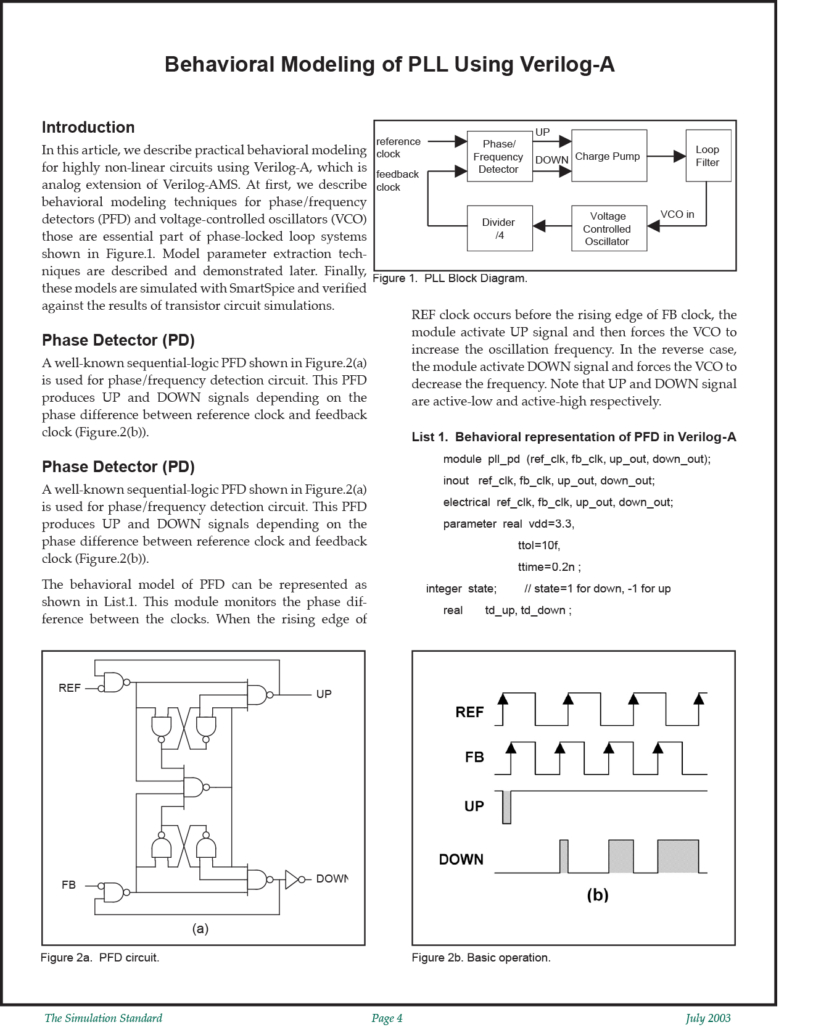

In this article, we describe practical behavioral modeling for highly non-linear circuits using Verilog-A, which is analog extension of Verilog-AMS. At first, we describe behavioral modeling techniques for phase/frequency detectors (PFD) and voltage-controlled oscillators (VCO) those are essential part of phase-locked loop systems shown in Figure.1. Model parameter extraction techniques are described and demonstrated later. Finally, these models are simulated with SmartSpice and verified against the results of transistor circuit simulations.

Using Binned Device Models with SmartSpice

Q. My simulation fails because SmartSpice cannot find a binned model, what does this mean?

HIPEX-Net: Hierarchical Layout Extractor for Expert Editor

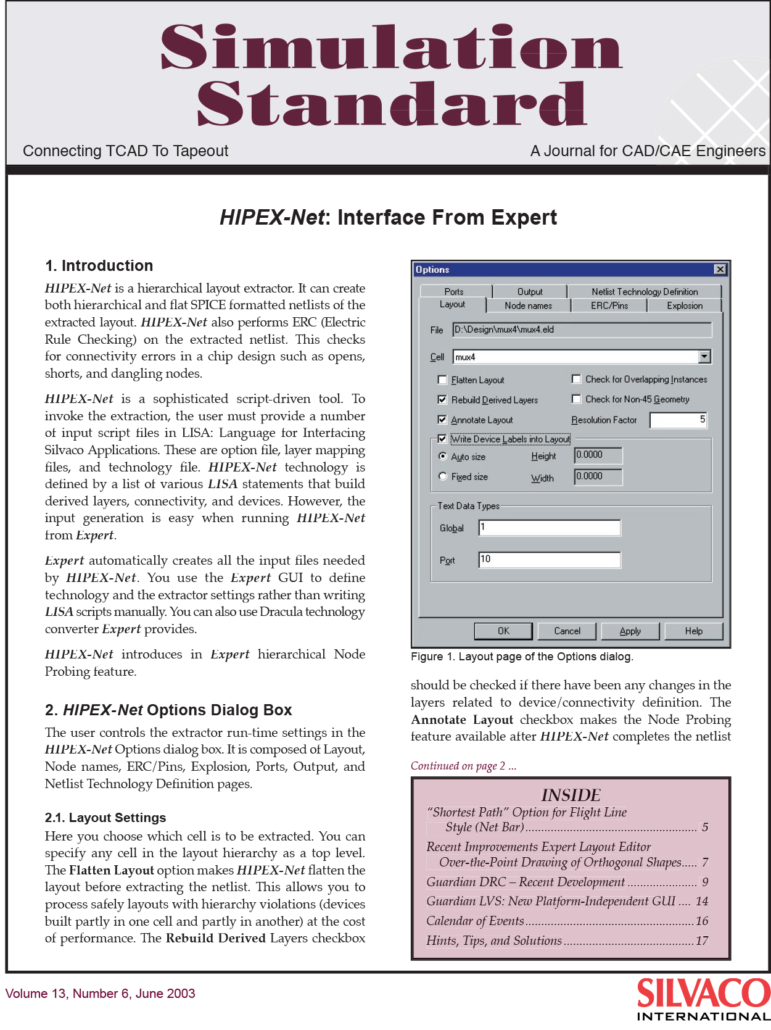

HIPEX-Net is a hierarchical layout extractor. It can create both hierarchical and flat SPICE formatted netlists of the extracted layout. HIPEX-Net also performs ERC (Electric Rule Checking) on the extracted netlist. This checks for connectivity errors in a chip design such as opens, shorts, and dangling nodes.

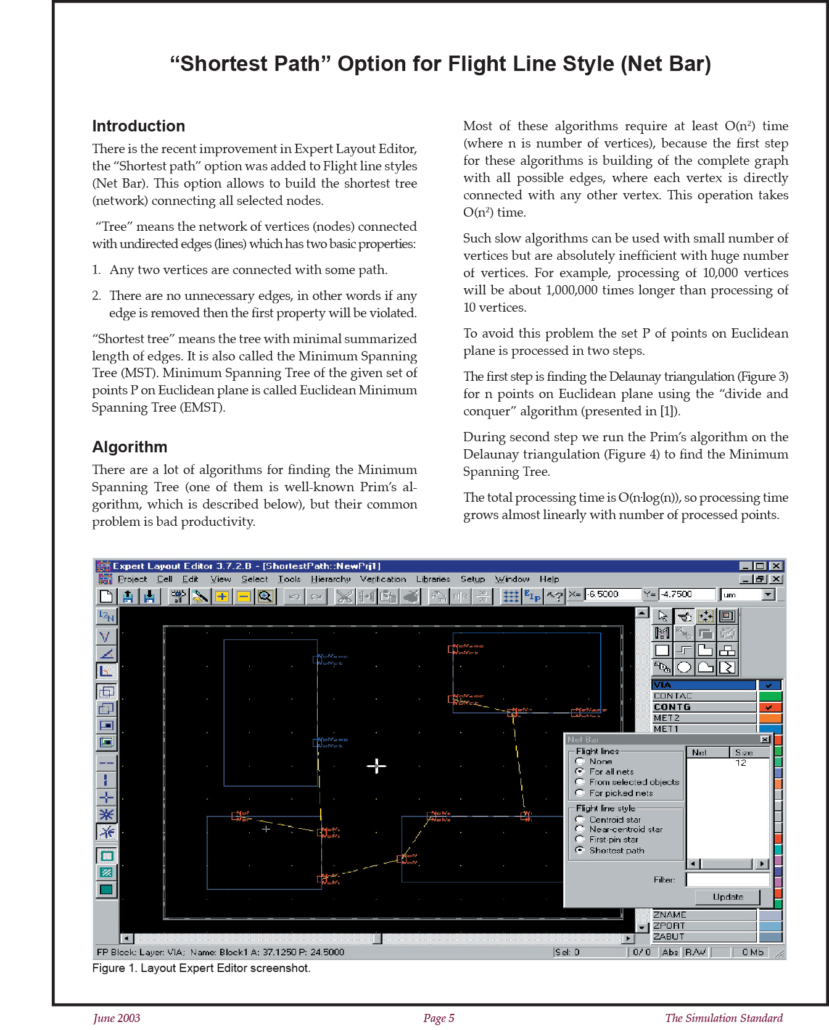

“Shortest Path” Option for Flight Line Style (Net Bar)

There is the recent improvement in Expert Layout Editor, the “Shortest path” option was added to Flight line styles (Net Bar). This option allows to build the shortest tree (network) connecting all selected nodes.

Expert Layout Editor Recent Improvements: Over-the-Point Drawing of Orthogonal Shapes

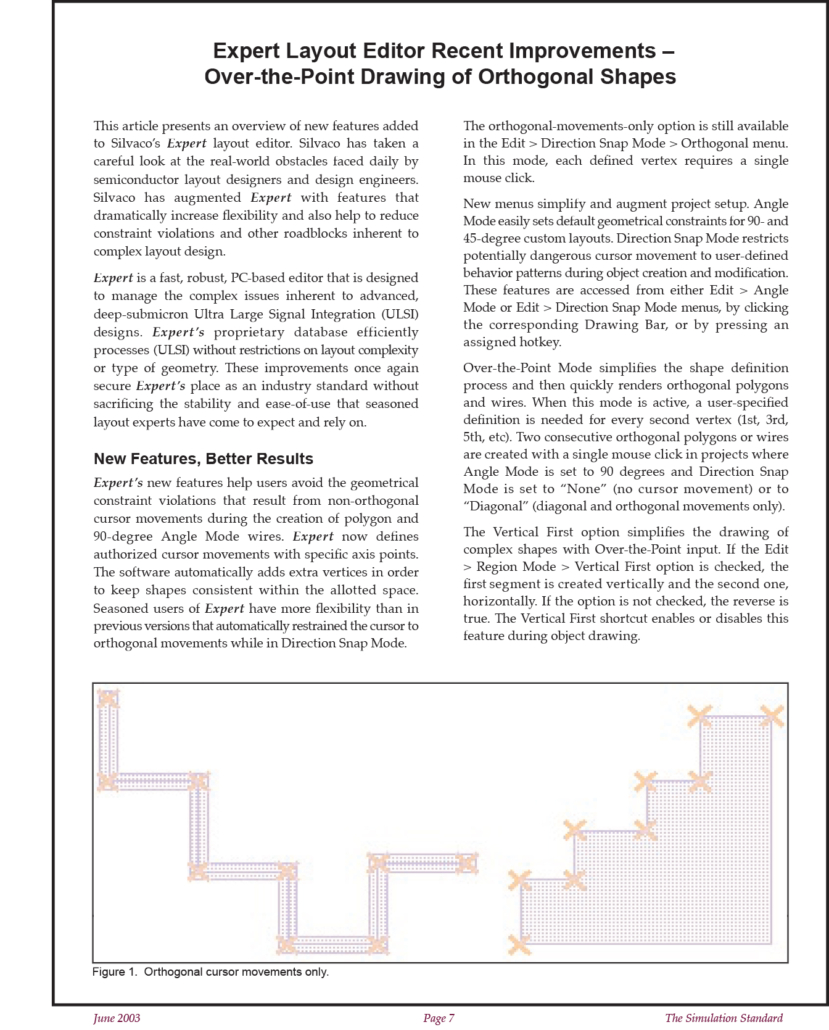

This article presents an overview of new features added to Silvaco's Expert layout editor. Silvaco has taken a careful look at the real-world obstacles faced daily by semiconductor layout designers and design engineers. Silvaco has augmented Expert with features that dramatically increase flexibility and also help to reduce constraint violations and other roadblocks inherent to complex layout design.

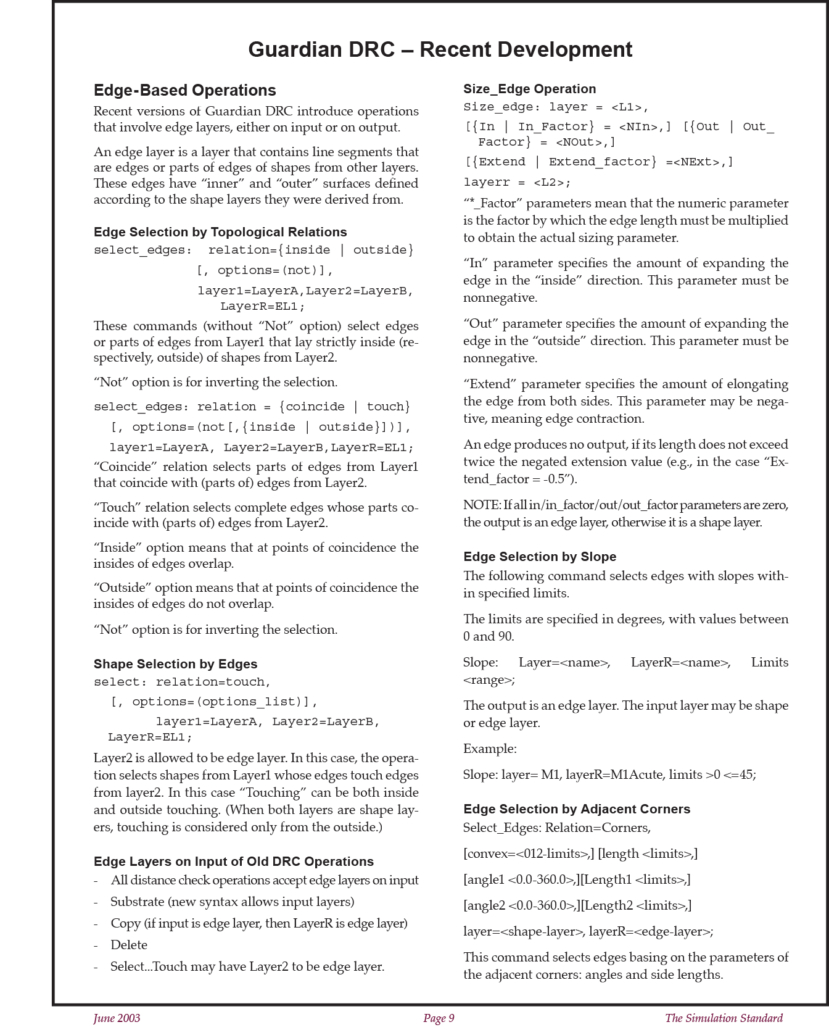

Guardian DRC Edge Layer Operations

Recent versions of Guardian DRC introduce operations that involve edge layers, either on input or on output. An edge layer is a layer that contains line segments that are edges or parts of edges of shapes from other layers. These edges have "inner" and "outer" surfaces defined according to the shape layers they were derived from.