Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

Topography Simulation of Trench Etch Using Monte Carlo Plasma Etch Model with Polymer Re-deposition

1. IntroductionThe topography simulation module, Elite has constantly been improved in order to simulate advanced processes, which are becoming more complex with device miniaturization and further integration of VLSI circuits. Elite is a two dimensional topography simulation module that works within ATHENA, and includes the etching and deposition models neccessary to simulate diverse modern technologies.

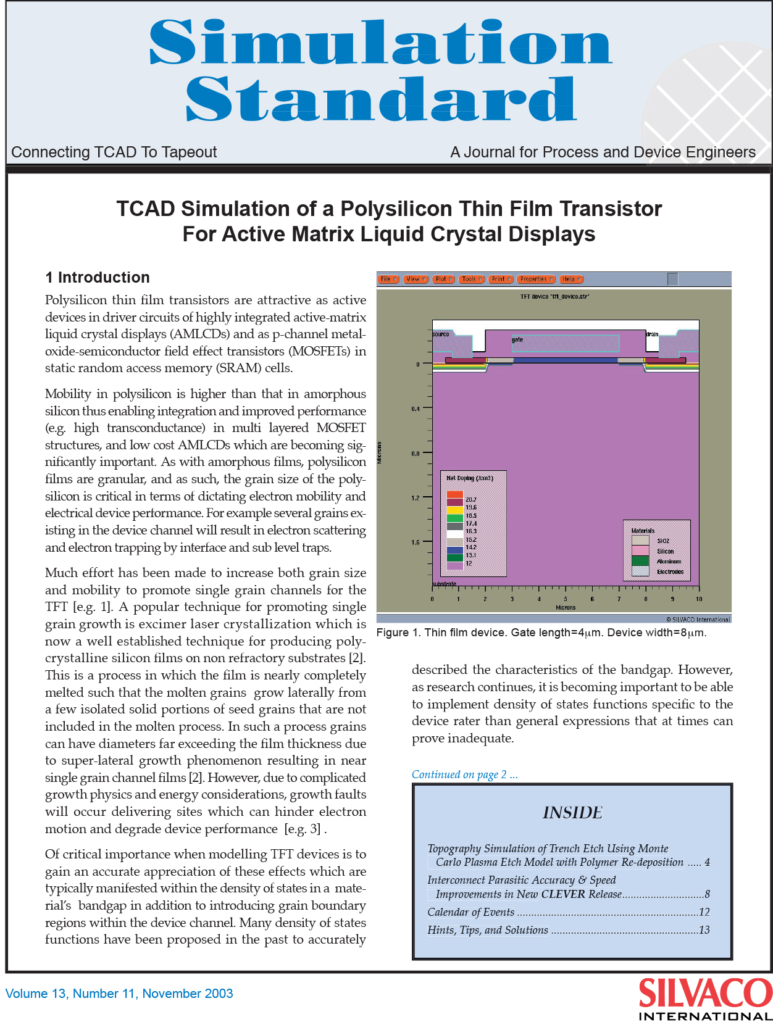

TCAD Simulation of a Polysilicon Thin Film Transistor For Active Matrix Liquid Crystal Displays

Polysilicon thin film transistors are attractive as active devices in driver circuits of highly integrated active-matrix liquid crystal displays (AMLCDs) and as p-channel metal-oxide-semiconductor field effect transistors (MOSFETs) in static random access memory (SRAM) cells.

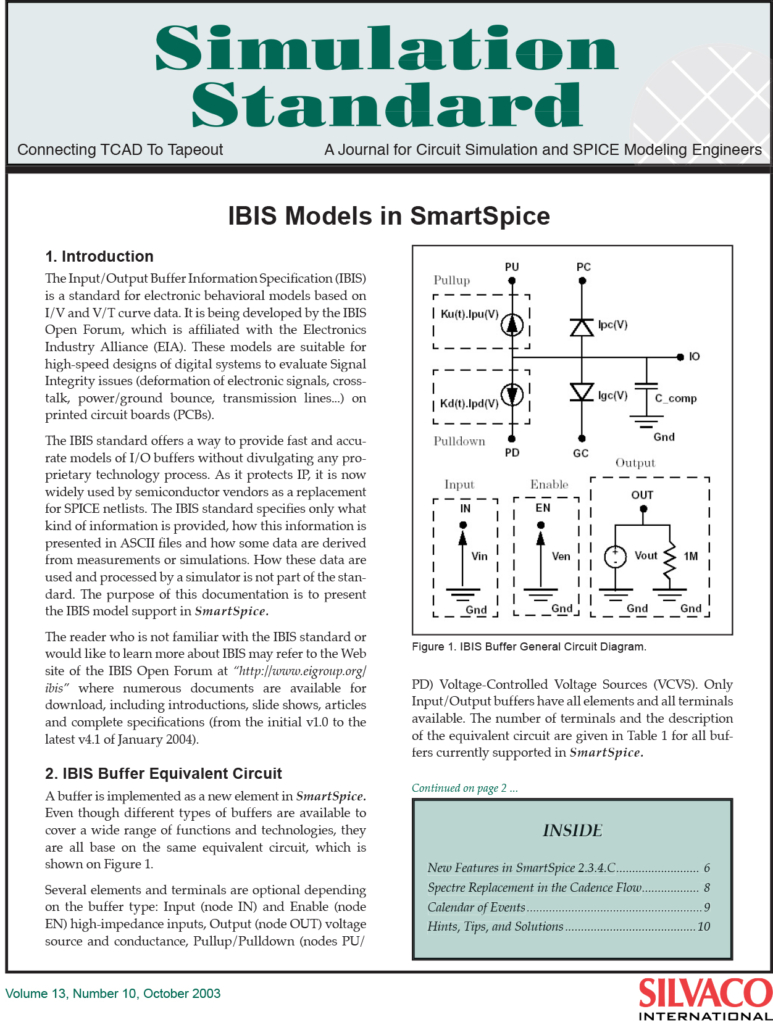

IBIS Models in SmartSpice

The Input/Output Buffer Information Specification (IBIS) is a standard for electronic behavioral models based on I/V and V/T curve data. It is being developed by the IBIS Open Forum, which is affiliated with the Electronics Industry Alliance (EIA). These models are suitable for high-speed designs of digital systems to evaluate Signal Integrity issues (deformation of electronic signals, cross-talk, power/ground bounce, transmission lines...) on printed circuit boards (PCBs).

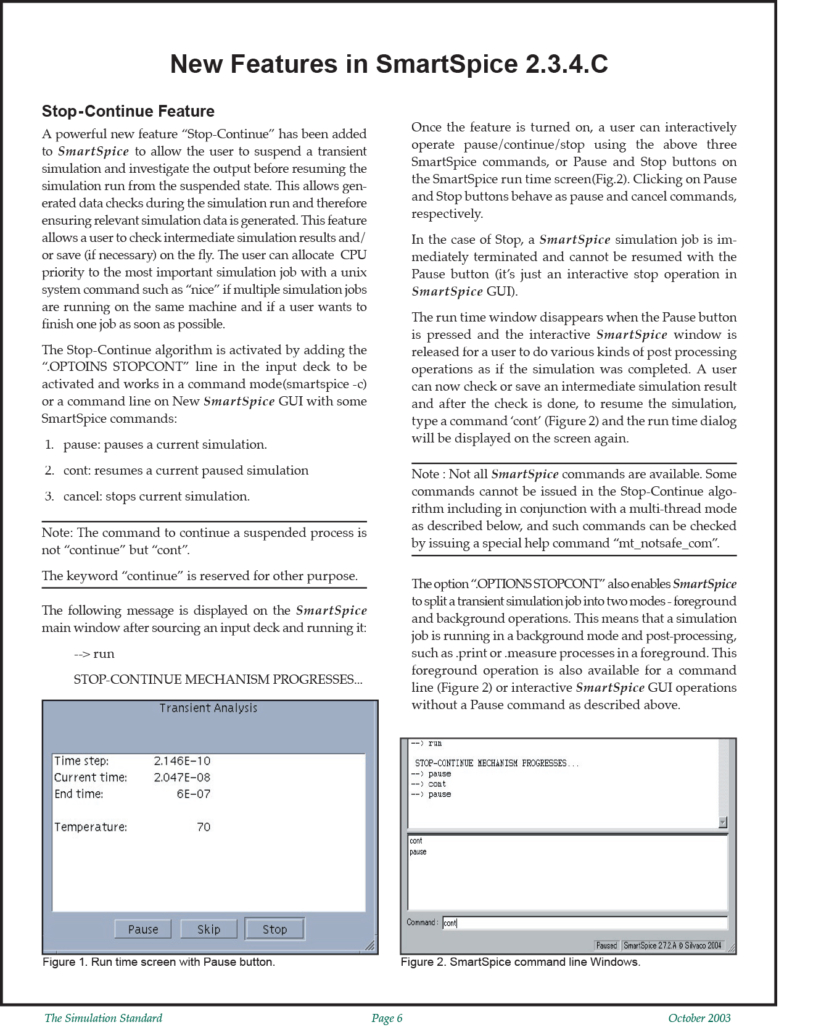

New Features in SmartSpice 2.3.4.C

A powerful new feature “Stop-Continue” has been added to SmartSpice to allow the user to suspend a transient simulation and investigate the output before resuming the simulation run from the suspended state. This allows generated data checks during the simulation run and therefore ensuring relevant simulation data is generated. This feature allows a user to check intermediate simulation results and/or save (if necessary) on the fly.

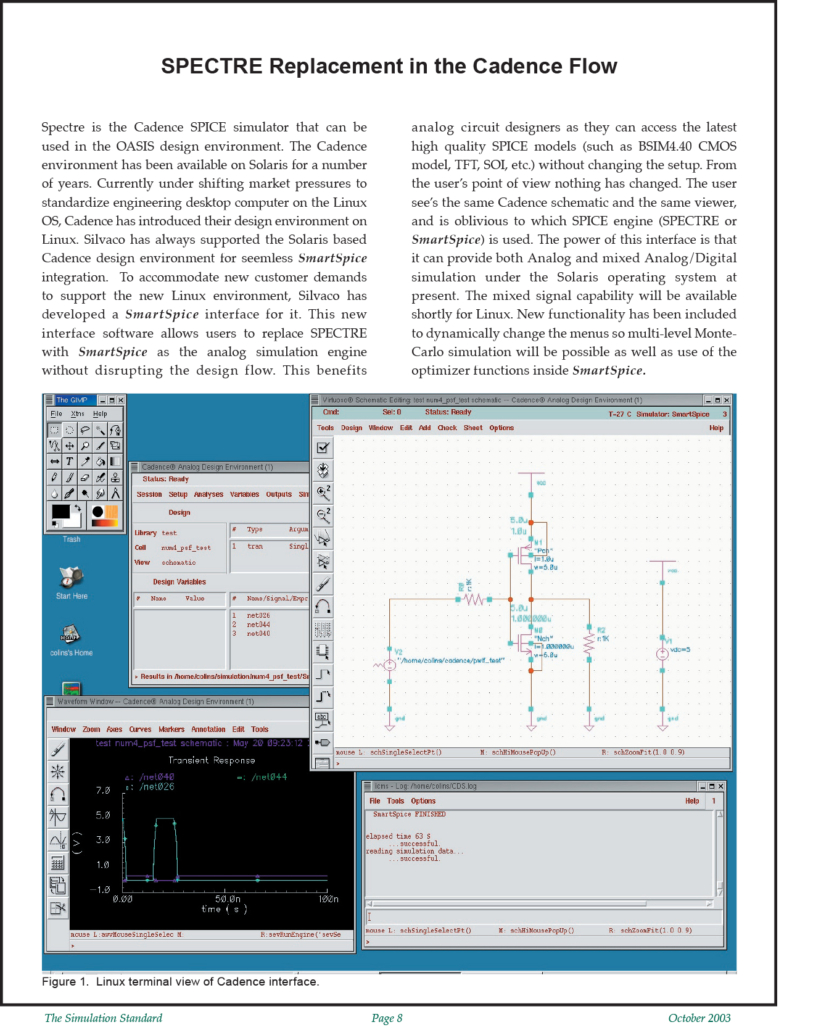

Spectre® Replacement in the Cadence Flow

Silvaco has always supported the Solaris based Cadence design environment for seemless SmartSpice integration. To accommodate new customer demands to support the new Linux environment, Silvaco has developed a SmartSpice interface for it. This new interface software allows users to replace Spectre with SmartSpice as the analog simulation engine without disrupting the design flow.

New Functionality – BUS notation in SmartSpice

A new notation has been introduced into SmartSpice to allow a compact expression of a multiple bit wire buss to be used. From this expression the user can simply state the members of a wire bus he wants to generate vectors for or probe. This syntax can be used in conjunction with .SAVE .PROBE