Simulation Standard Technical Journal

A Journal for Process and Device Engineers

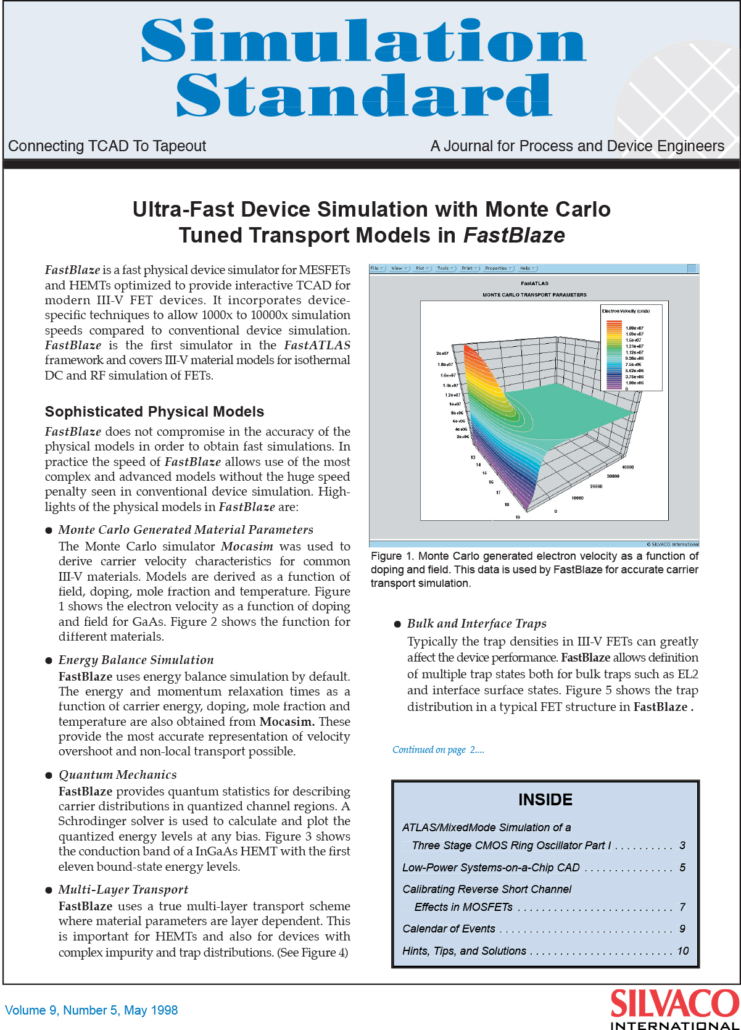

Ultra-Fast Device Simulation with Monte Carlo Tuned Transport Models in FastBlaze

FastBlaze is a fast physical device simulator for MESFETs and HEMTs optimized to provide interactive TCAD for modern III-V FET devices. It incorporates device-specific techniques to allow 1000x to 10000x simulation speeds compared to conventional device simulation.

HINTS & TIPS – April 1998

Q. What is the typical method of measuring flicker noise using S3245A Noise Amplifier?

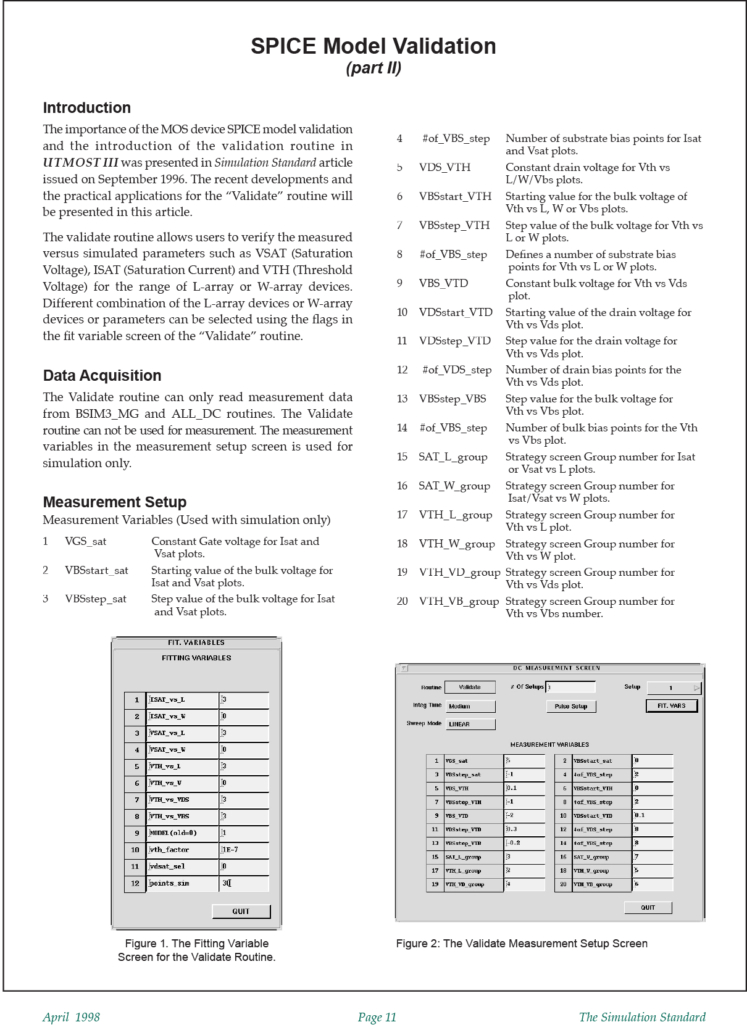

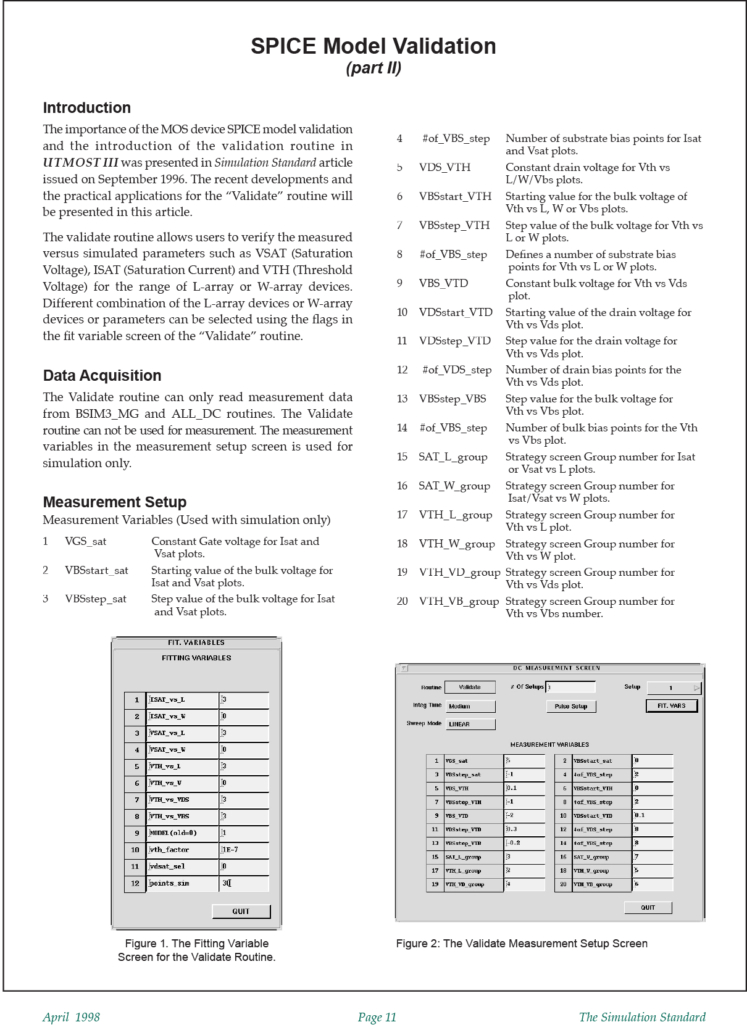

SPICE Model Validation

The importance of the MOS device SPICE model validation and the introduction of the validation routine in UTMOST III was presented in Simulation Standard article issued on September 1996. The recent developments and the practical applications for the "Validate" routine will be presented in this article.

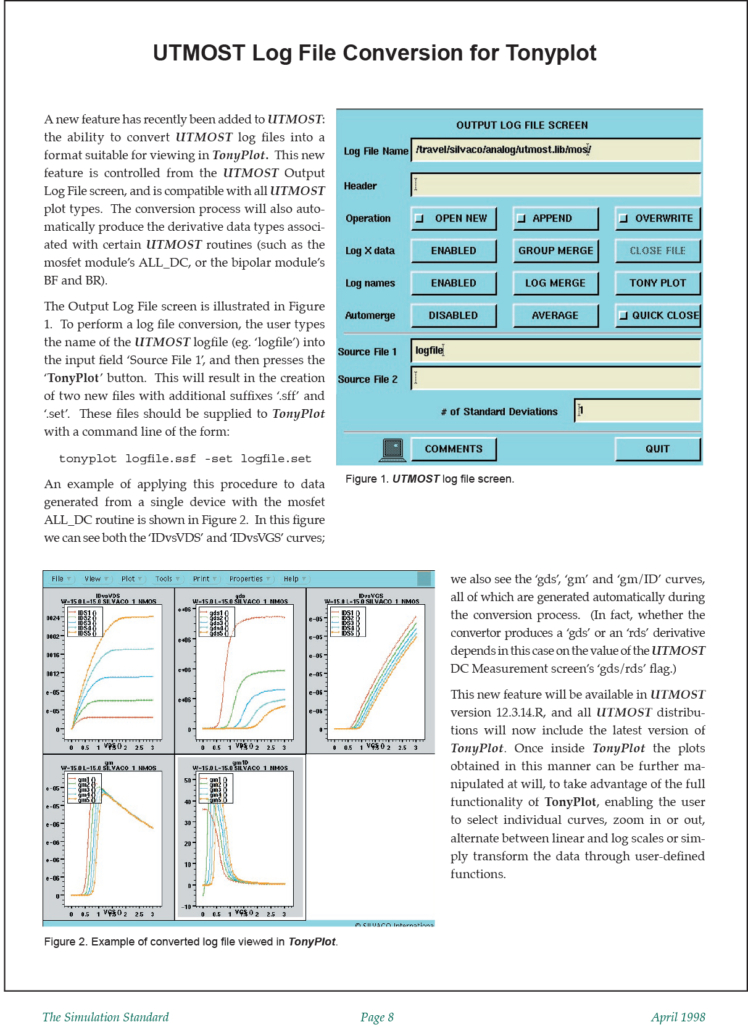

UTMOST Log File Conversion for TonyPlot

A new feature has recently been added to UTMOST: the ability to convert UTMOST log files into a format suitable for viewing in TonyPlot. This new feature is controlled from the UTMOST Output Log File screen, and is compatible with all UTMOST plot types. The conversion process will also automatically produce the derivative data types associated with certain UTMOST routines (such as the mosfet module's ALL_DC, or the bipolar module's BF and BR).

Advanced Cell Characterization Using SmartSpice Scripting Features

In a previous article [1], the efficient use of the SmartSpice .MODIF statement for cell characterization was discussed. This article will focus on using advanced features of the SmartSpice scripting language to solve this problem in a more flexible manner.

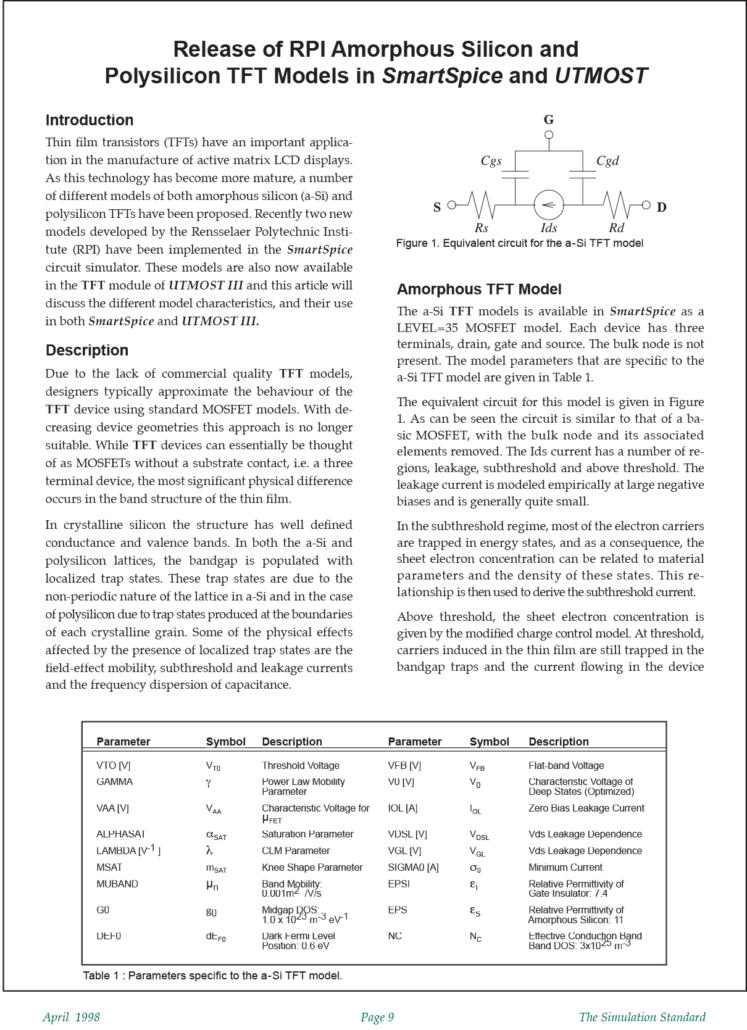

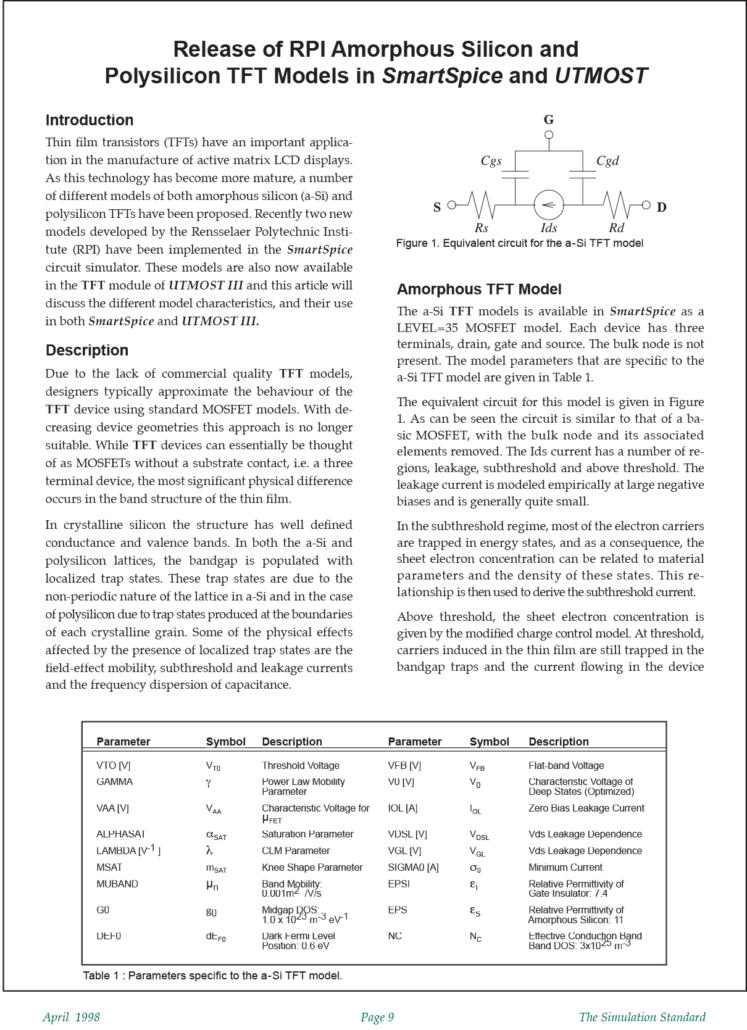

Release of RPI Amorphous Silicon and Polysilicon TFT Models in SmartSpice and UTMOST

Thin film transistors (TFTs) have an important application in the manufacture of active matrix LCD displays. As this technology has become more mature, a number of different models of both amorphous silicon (a-Si) and polysilicon TFTs have been proposed. Recently two new models developed by the Rensselaer Polytechnic Institute (RPI) have been implemented in the SmartSpice circuit simulator. These models are also now available in the TFT module of UTMOST III and this article will discuss the different model characteristics, and their use in both SmartSpice and UTMOST III.