Simulation Standard Technical Journal

A Journal for Process and Device Engineers

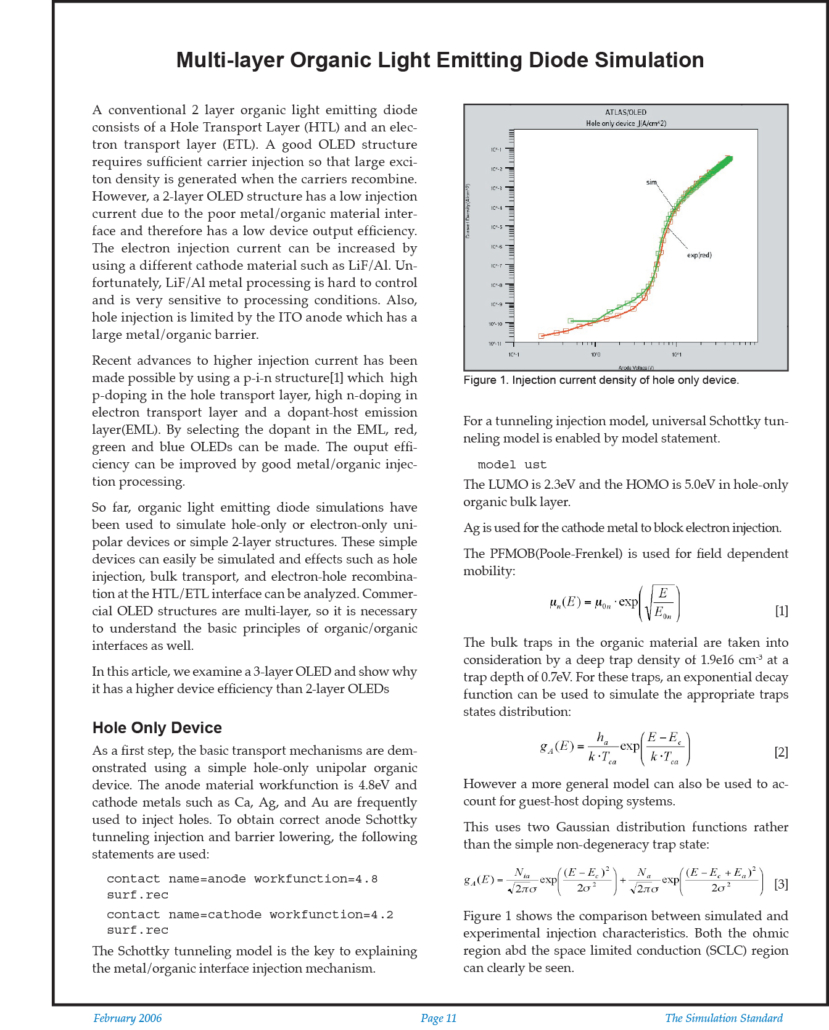

Multi-layer Organic Light Emitting Diode Simulation

A conventional 2 layer organic light emitting diode consists of a Hole Ttransport Layer (HTL) and an electron transport layer (ETL). A good OLED structure requires sufficient carrier injection so that large exciton density is generated when the carriers recombine. However, a 2-layer OLED structure has a low injection current due to the poor metal/organic material interface and therefore has a low device output efficiency. The electron injection current can be increased by using a different cathode material such as LiF/Al. Unfortunately, LiF/Al metal processing is hard to control and is very sensitive to processing conditions. Also, hole injection is limited by the ITO anode which has a large metal/organic barrier.

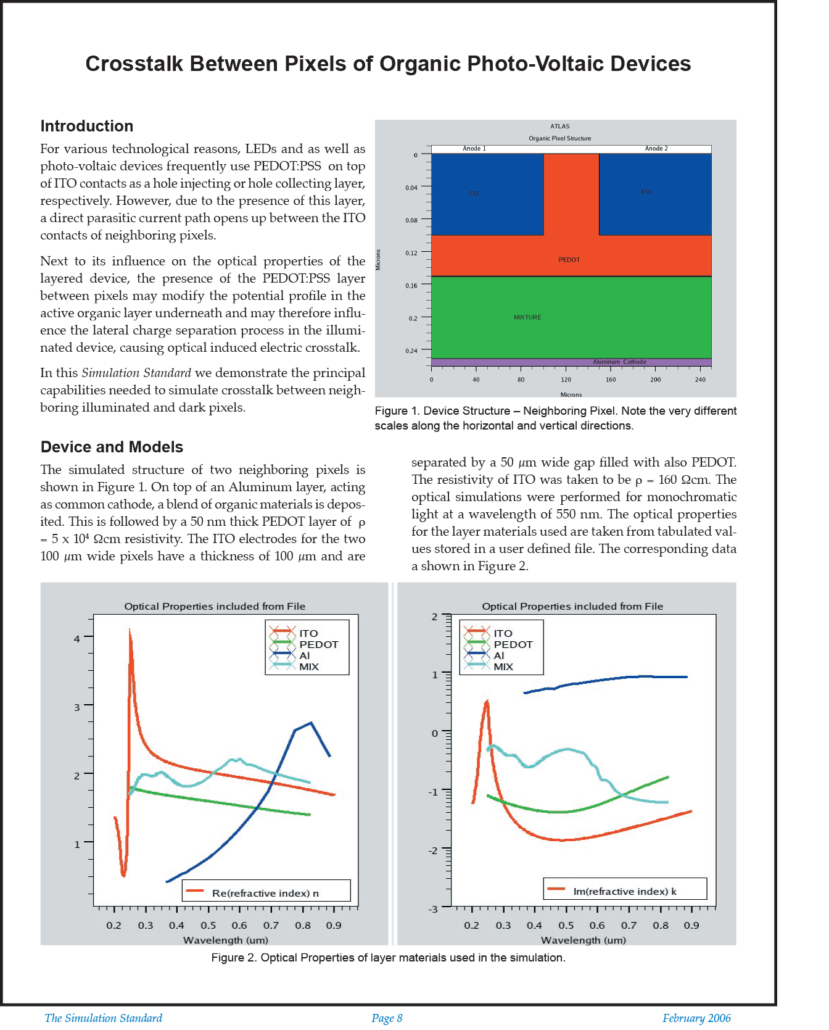

Crosstalk Between Pixels of Organic Photo-Voltaic Devices

For various technological reasons, LEDs and as well as photo-voltaic devices frequently use PEDOT:PSS on top of ITO contacts as a hole injecting or hole collecting layer, respectively. However, due to the presence of this layer, a direct parasitic current path opens up between the ITO contacts of neighboring pixels.

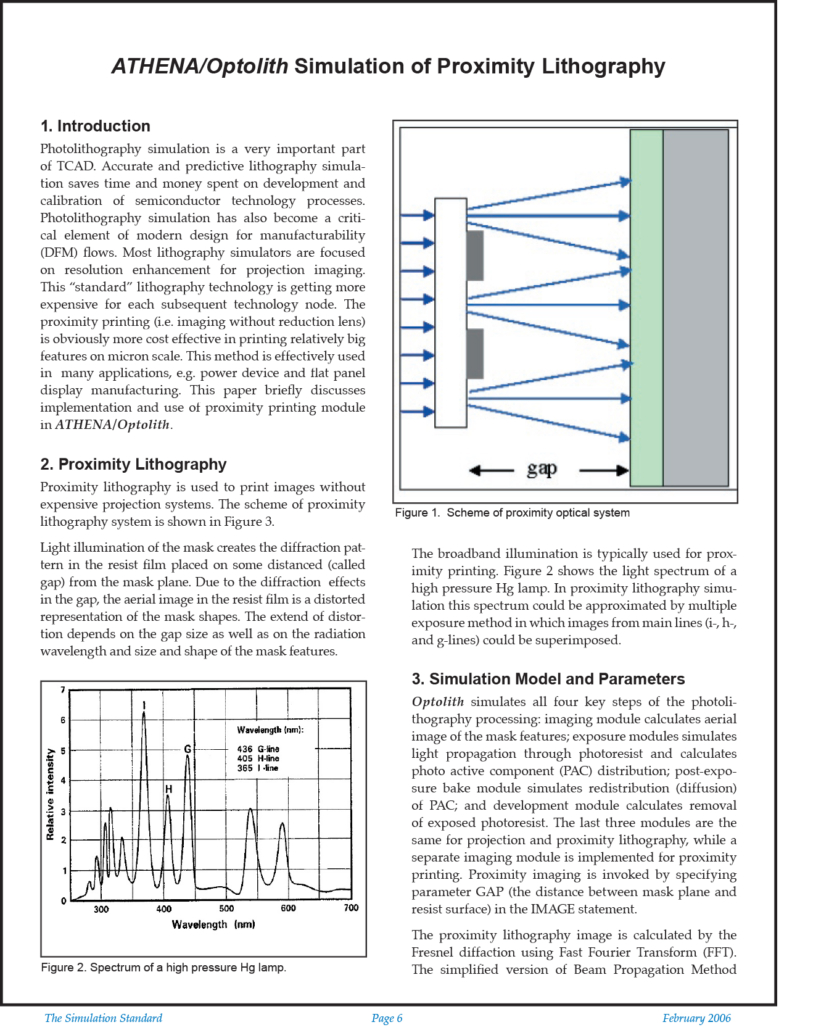

Athena/Optolith Simulation of Proximity Lithography

Photolithography simulation is a very important part of TCAD. Accurate and predictive lithography simulation saves time and money spent on development and calibration of semiconductor technology processes.

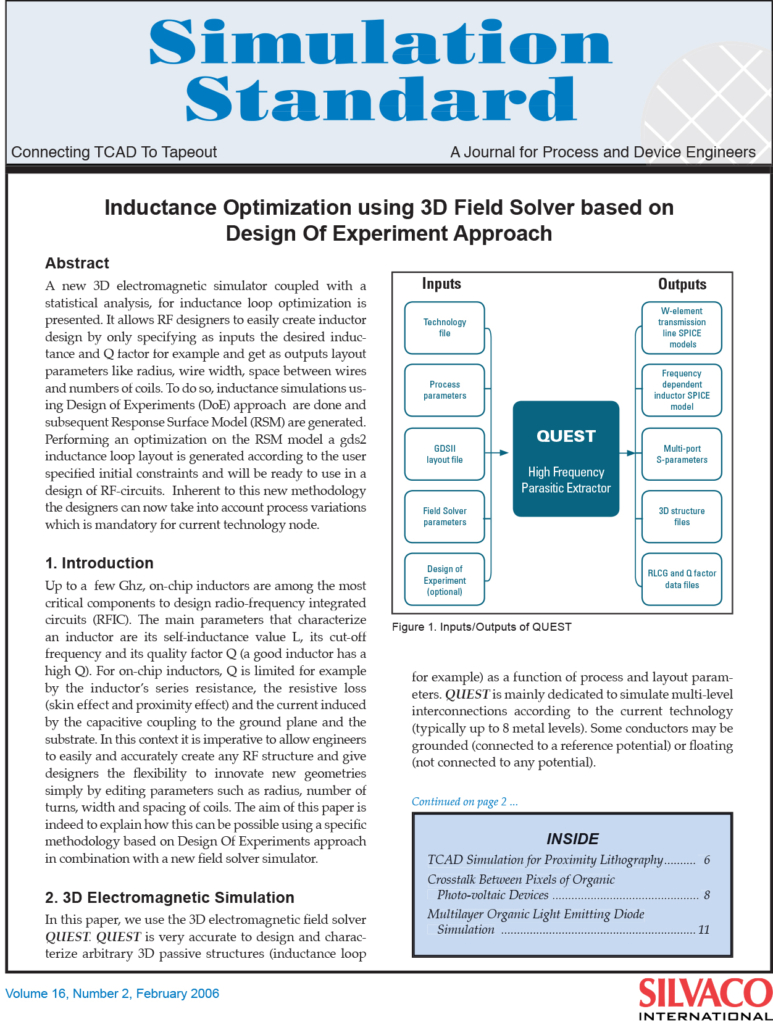

Inductance Optimization using 3D Field Solver based on Design Of Experiment Approach

A new 3D electromagnetic simulator coupled with a statistical analysis, for inductance loop optimization is presented. It allows RF designers to easily create inductor design by only specifying as inputs the desired inductance and Q factor for example and get as outputs layout parameters like radius

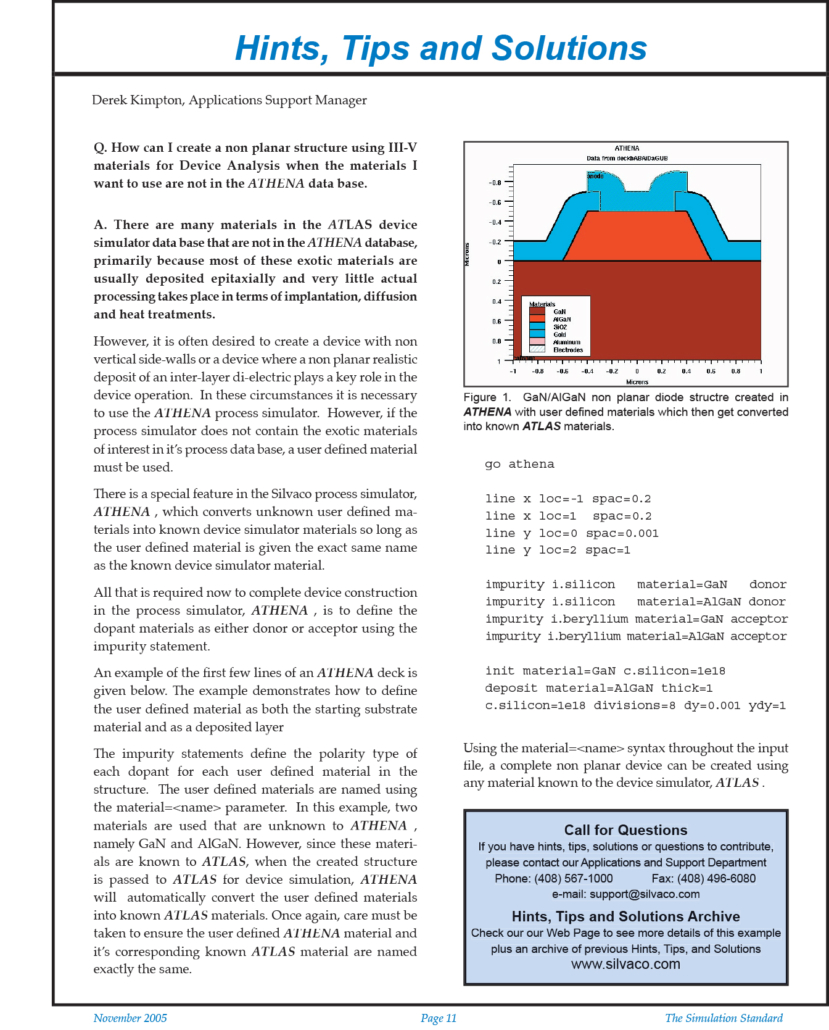

How can I create a non planar structure using III-V materials for Device Analysis

How can I create a non planar structure using III-V materials for Device Analysis when the materials I want to use are not in the ATHENA data base.

Numerical Analysis of GaInP Solar Cells: Toward Advanced Photovoltaic Devices Modeling

Simulation capacities of GaInP solar cells were studied with a special emphasis on material and structural parameters. The comparison between experimental and numerical results allowed to validate the models used for such a device and permitted to extrapolate the layers structure. With this method we proved the role of the substrate in the simulation and thus its importance in the optimization process. This study is an important previous step to validate the numerical approach for multi-junction solar cell simulation in 3D.