Simulation Standard Technical Journal

A Journal for Process and Device Engineers

Simulating the Hysteresis effects of Si/SiO2 Interface Traps

The trap states at the interface of Silicon with Silicon Dioxide are usually divided conceptually into interface states and fixed oxide charges [1]. These trap states can cause the degradation of the performance of devices such as MOSFETs, when they are stressed into a regime where hot carriers are significant. This degradation is usually permanent and occurs for stress times of the order of 103 seconds [2]. This phenomenon is well studied, and ATLAS has a degradation model for simulating these effects [3].

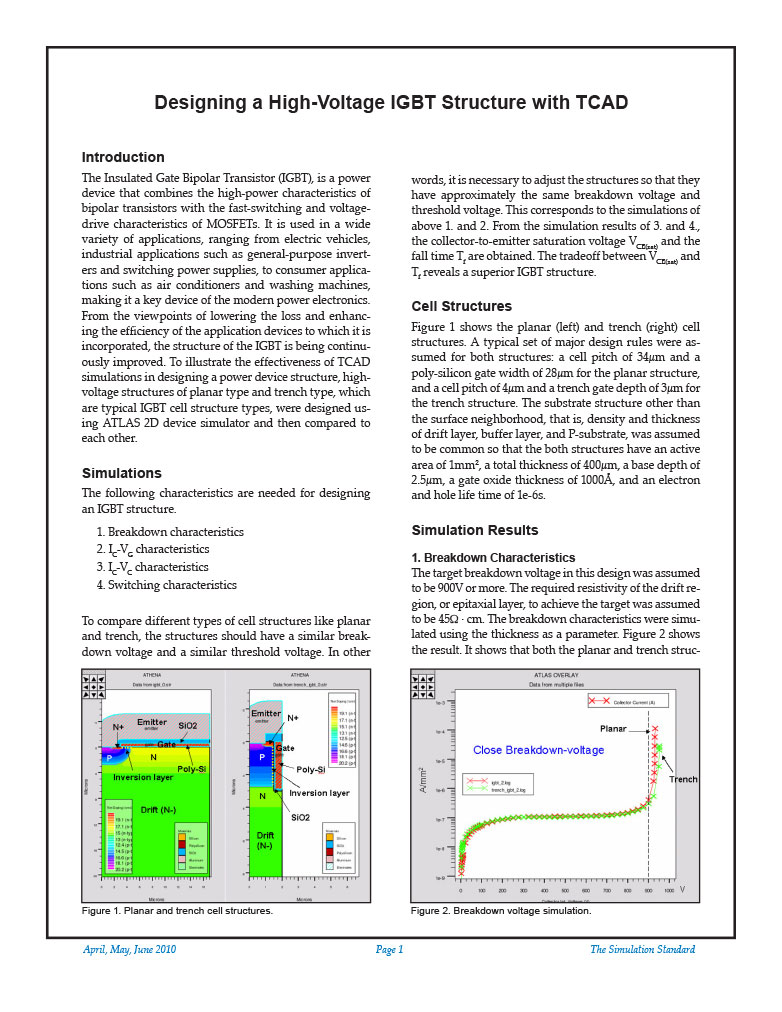

Designing a High-Voltage IGBT Structure with TCAD

The Insulated Gate Bipolar Transistor (IGBT), is a power device that combines the high-power characteristics of bipolar transistors with the fast-switching and voltage-drive characteristics of MOSFETs. It is used in a wide variety of applications, ranging from electric vehicles, industrial applications such as general-purpose inverters and switching power supplies, to consumer applications such as air conditioners and washing machines, making it a key device of the modern power electronics. From the viewpoints of lowering the loss and enhancing the efficiency of the application devices to which it is incorporated, the structure of the IGBT is being continuously improved. To illustrate the effectiveness of TCAD simulations in designing a power device structure, high-voltage structures of planar type and trench type, which are typical IGBT cell structure types, were designed using ATLAS 2D device simulator and then compared to each other.

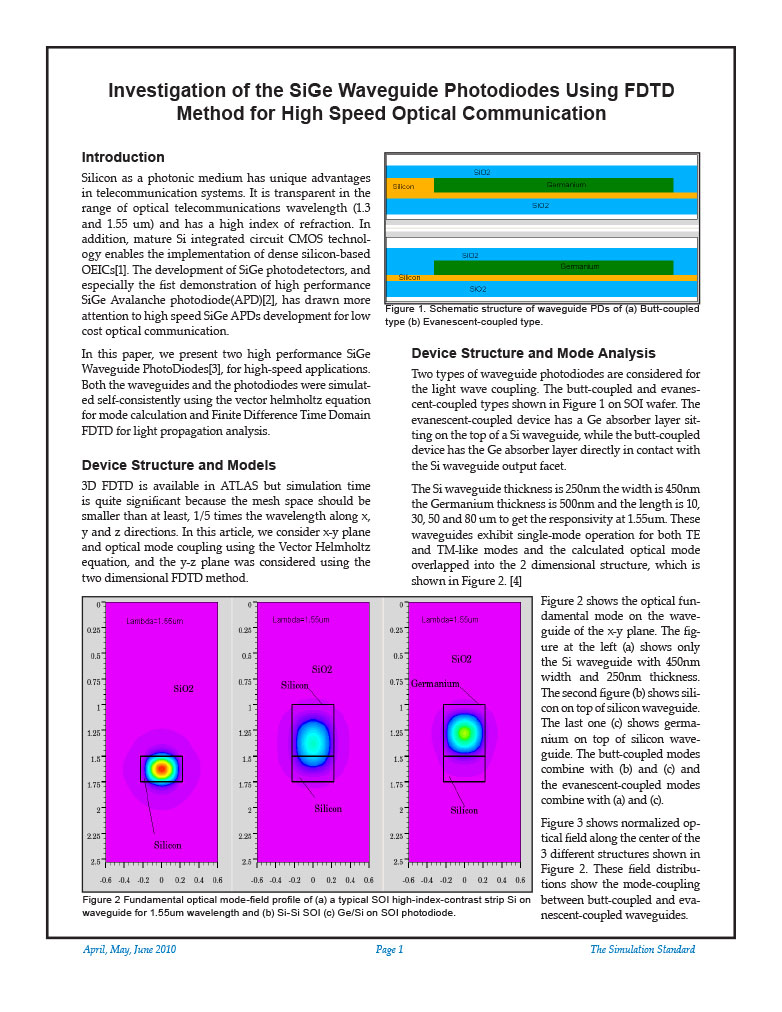

Investigation of the SiGe Waveguide Photodiodes Using FDTD Method for High Speed Optical Communication

Silicon as a photonic medium has unique advantages in telecommunication systems. It is transparent in the range of optical telecommunications wavelength (1.3 and 1.55 um) and has a high index of refraction. In addition, mature Si integrated circuit CMOS technology enables the implementation of dense silicon-based OEICs. The development of SiGe photodetectors, and especially the fist demonstration of high performance SiGe Avalanche photodiode(APD)[1], has drawn more attention to high speed SiGe APDs development for low cost optical communication.

A Box Method Discretisation for the Drift-Diffusion Equations in a Magnetic Field

The problem of discretising the semiconductor drift-diffusion equations in the presence of a uniform magnetic field using the Box Method has previously been addressed in the literature. For the case of a rectangular non-uniform grid in 2D see[1], and for a general triangular mesh see[2]. These methods have also been extended to 3D [3],[4]. We have implemented and analysed these methods and found them all to be flawed in some way. In this paper we describe the established discretisations and elaborate on their flaws. We then briefly describe the new discretisation developed by Silvaco, and give some examples of its use.

Simulation of Resonant Tunneling Diodes Using ATLAS

This article describes a model for Resonant Tunneling Diodes (RTDs) implemented within ATLAS framework. The model is based on a self-consistent solution of Poisson and Non-Equilibrium Green’s Function (NEGF) equations with an effective mass Hamiltonian. Simulation results are presented for generic GaAs and SiGe RTDs.

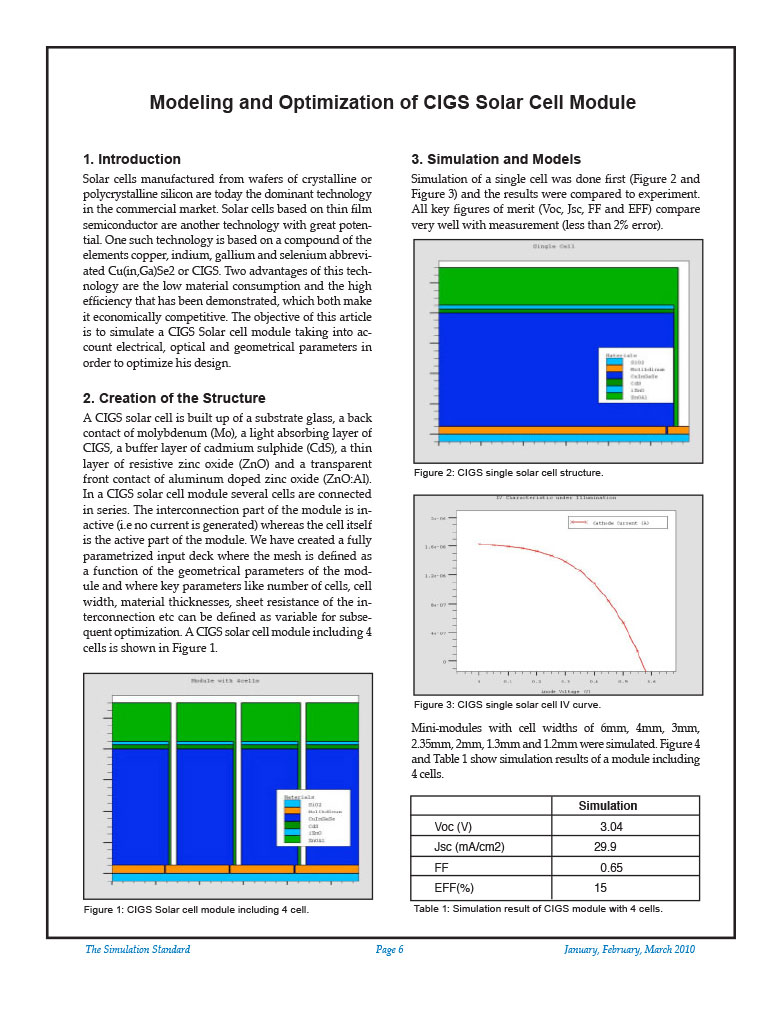

Modeling and Optimization of CIGS Solar Cell Module

Solar cells manufactured from wafers of crystalline or polycrystalline silicon are today the dominant technology in the commercial market. Solar cells based on thin film semiconductor are another technology with great potential. One such technology is based on a compound of the elements copper, indium, gallium and selenium abbreviated Cu(in,Ga)Se2 or CIGS. Two advantages of this technology are the low material consumption and the high efficiency that has been demonstrated, which both make it economically competitive. The objective of this article is to simulate a CIGS Solar cell module taking into account electrical, optical and geometrical parameters in order to optimize his design.