Simulation Standard

Silvaco面向半导体工艺和器件仿真工程师推出的技术刊物

Hints & Tips September 1999

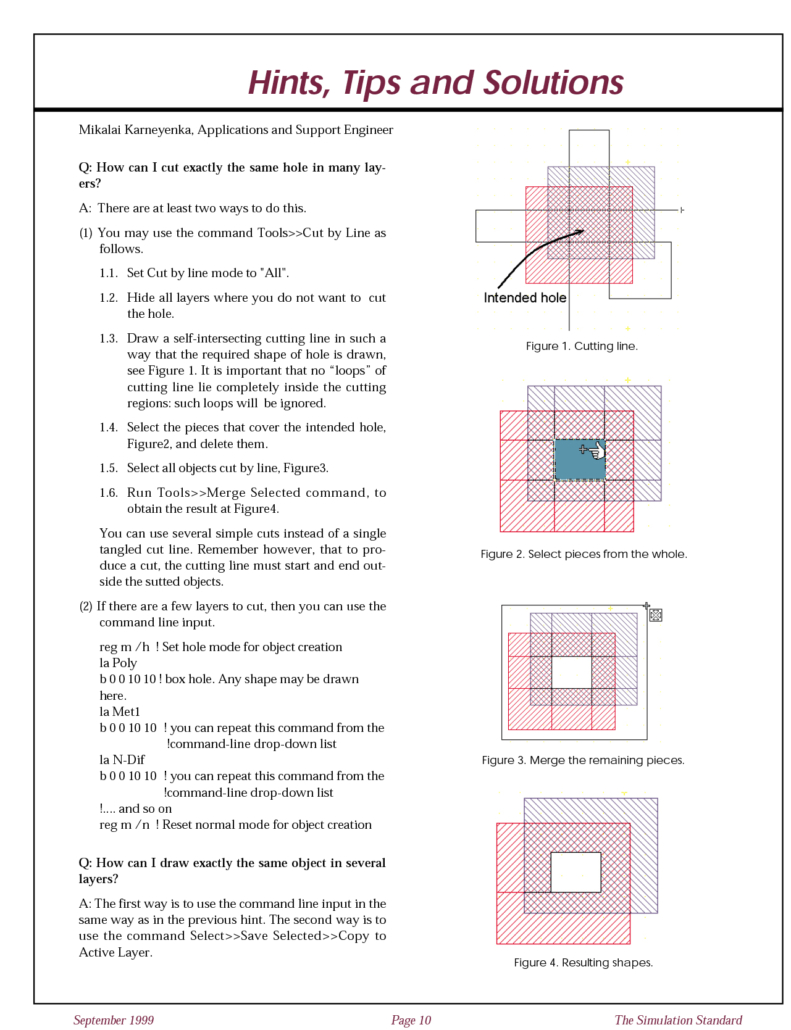

Q: How can I cut exactly the same hole in many layers? A: There are at least two ways to do this. (1) You may use the command Tools>>Cut by Line as follows.

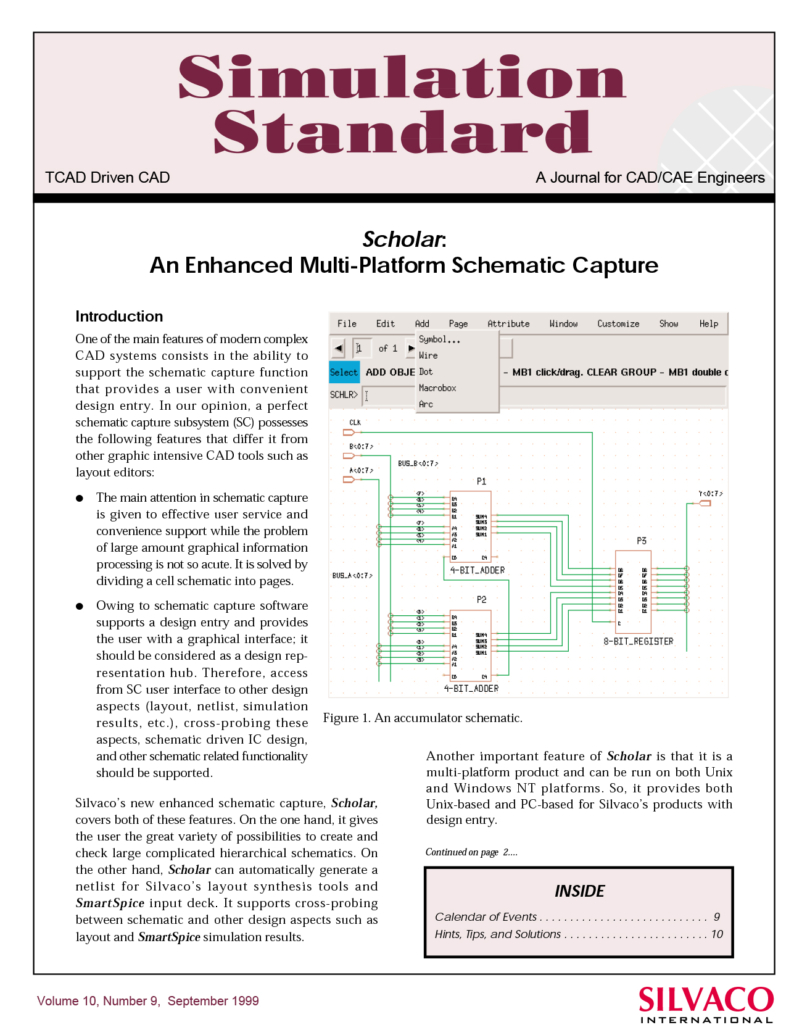

Scholar: An Enhanced Multi-Platform Schematic Capture

One of the main features of modern complex CAD systems consists in the ability to support the schematic capture function that provides a user with convenient design entry. In our opinion, a perfect schematic capture subsystem (SC) possesses the following features that differ it from other graphic intensive CAD tools such as layout editors:

Hints & Tips August 1999

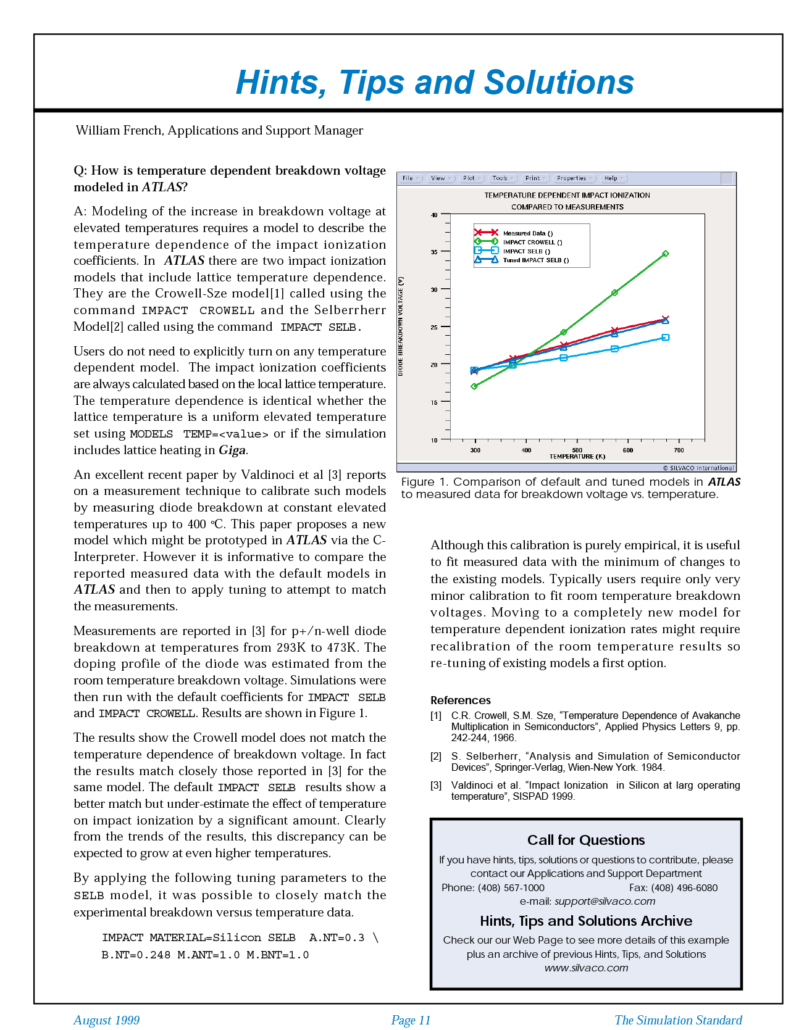

A: Modeling of the increase in breakdown voltage at elevated temperatures requires a model to describe the temperature dependence of the impact ionization coefficients. In ATLAS there are two impact ionization models that include lattice temperature dependence. They are the Crowell-Sze model[1] called using the command IMPACT CROWELL and the Selberrherr Model[2] called using the command IMPACT SELB.

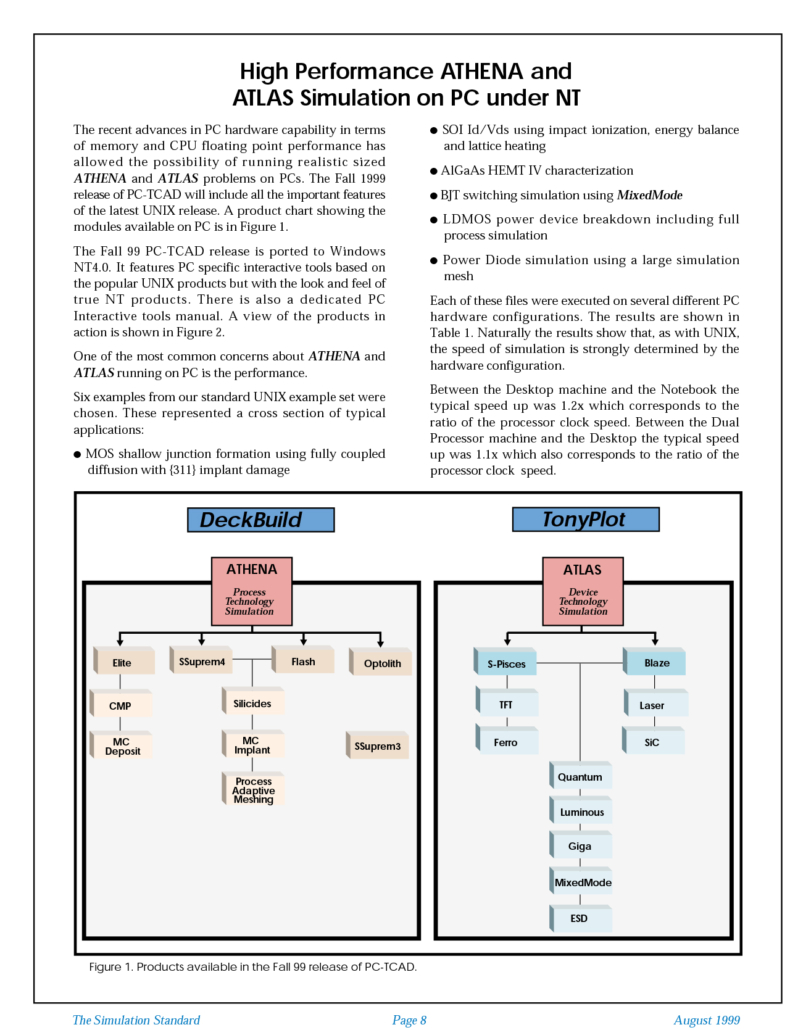

High Performance ATHENA and ATLAS Simulation on PC under NT

The recent advances in PC hardware capability in terms of memory and CPU floating point performance has allowed the possibility of running realistic sized ATHENA and ATLAS problems on PCs. The Fall 1999 release of PC-TCAD will include all the important features of the latest UNIX release. A product chart showing the modules available on PC is in Figure 1.

New Thermionic Emission and Tunneling Models in ATLAS

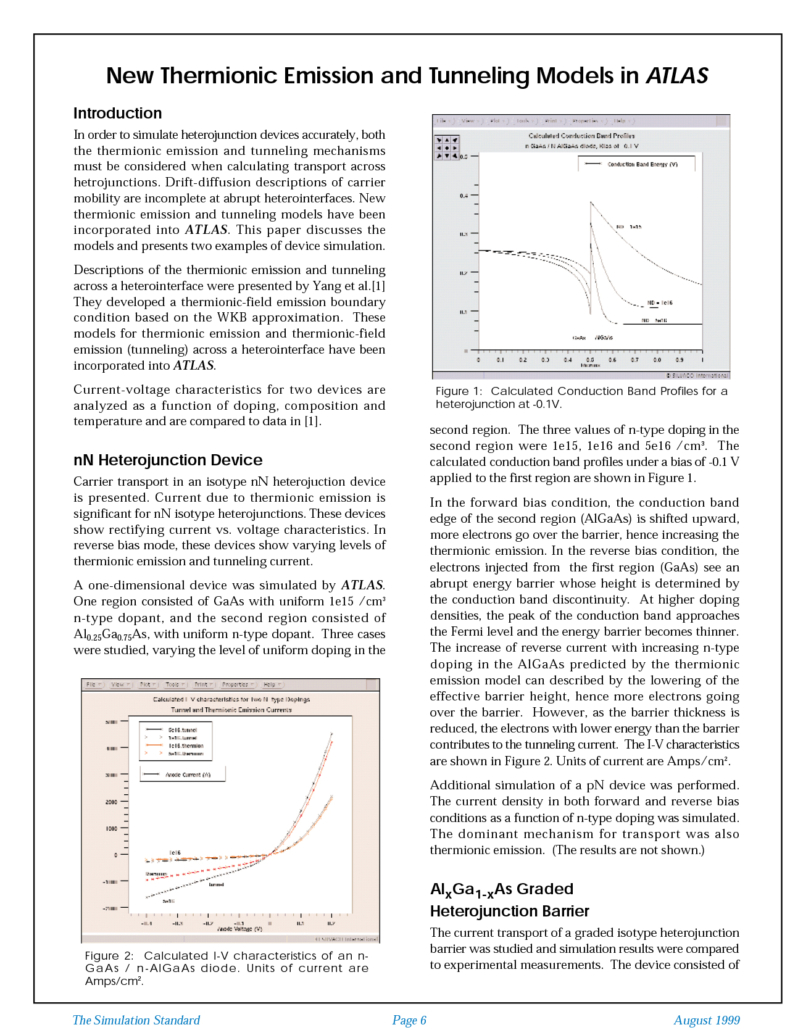

In order to simulate heterojunction devices accurately, both the thermionic emission and tunneling mechanisms must be considered when calculating transport across hetrojunctions. Drift-diffusion descriptions of carrier mobility are incomplete at abrupt heterointerfaces. New thermionic emission and tunneling models have been incorporated into ATLAS. This paper discusses the models and presents two examples of device simulation.

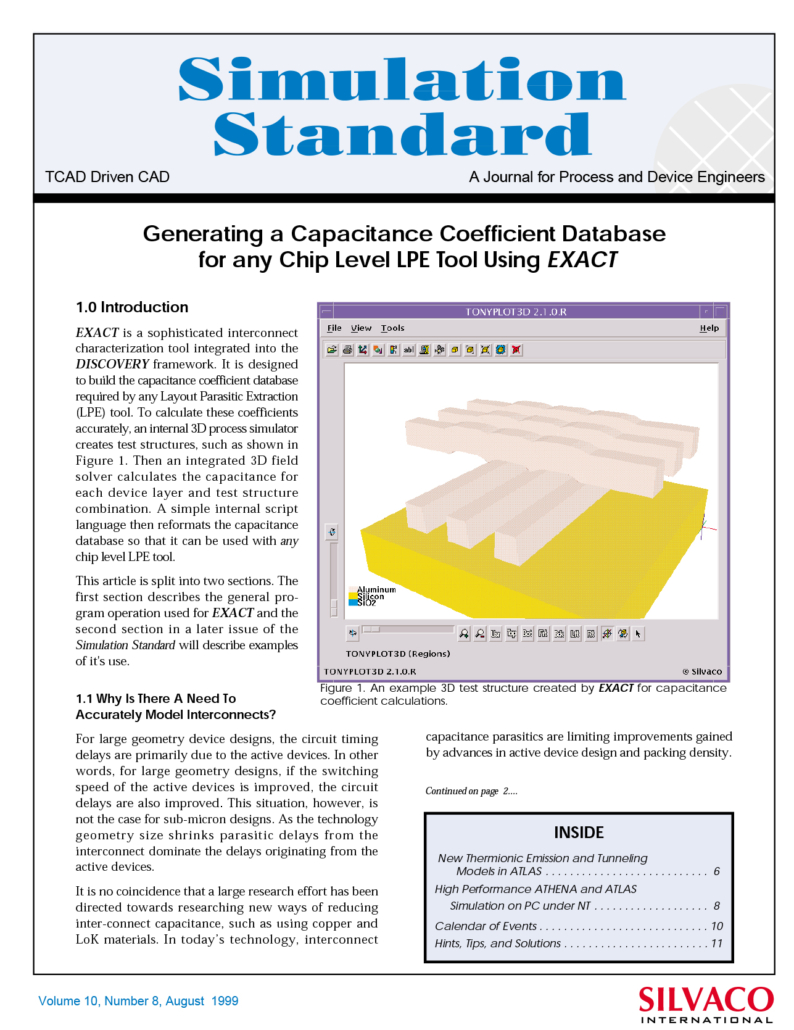

Generating a Capacitance Coefficient Database for any Chip Level LPE Tool Using EXACT

EXACT is a sophisticated interconnect characterization tool integrated into the DISCOVERY framework. It is designed to build the capacitance coefficient database required by any Layout Parasitic Extraction (LPE) tool. To calculate these coefficients accurately, an internal 3D process simulator creates test structures, such as shown in Figure 1. Then an integrated 3D field solver calculates the capacitance for each device layer and test structure combination. A simple internal script language then reformats the capacitance database so that it can be used with any chip level LPE tool.