Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

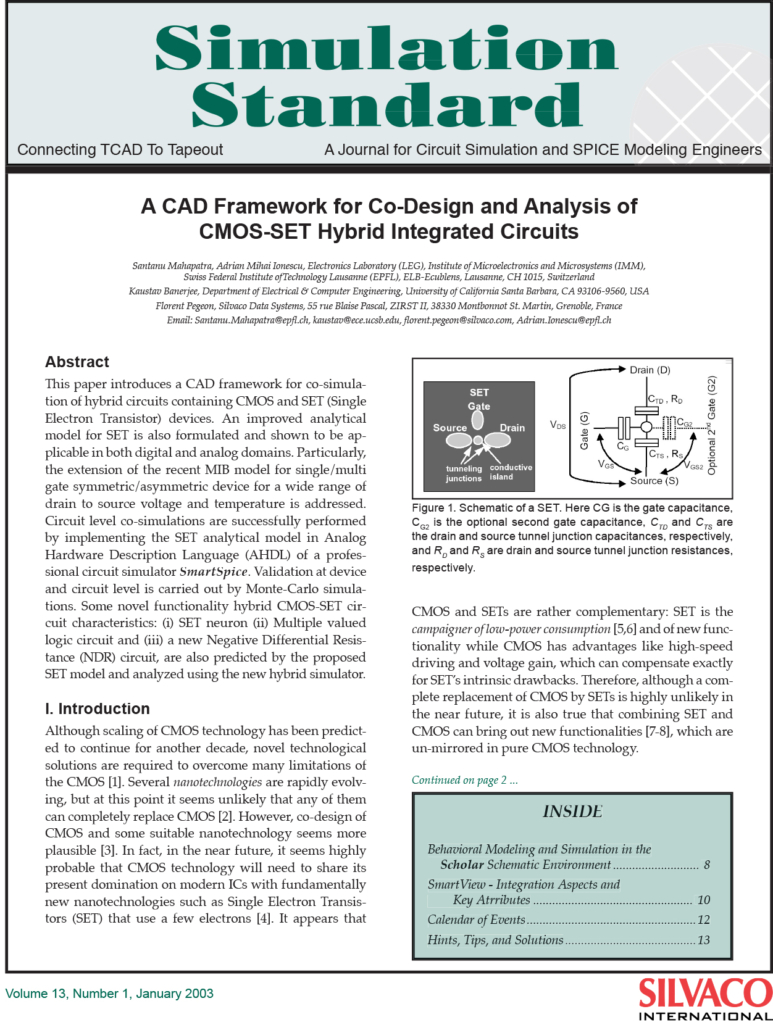

A CAD Framework for Co-Design and Analysis of CMOS-SET Hybrid Integrated Circuits

This paper introduces a CAD framework for co-simulation of hybrid circuits containing CMOS and SET (Single Electron Transistor) devices. An improved analytical model for SET is also formulated and shown to be applicable in both digital and analog domains.

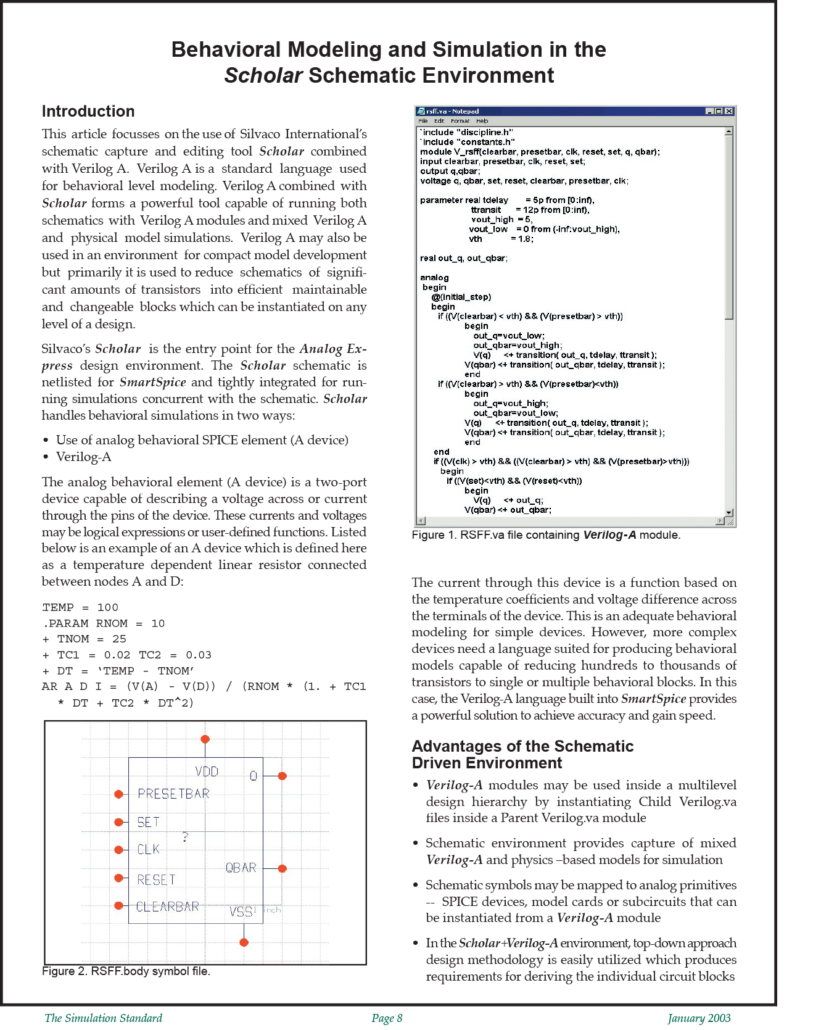

Behavioral Modeling and Simulation in the Scholar Schematic Environment

This article focusses on the use of Silvaco International’s schematic capture and editing tool Scholar combined with Verilog A. Verilog A is a standard language used for behavioral level modeling. Verilog A combined with Scholar forms a powerful tool capable of running both schematics with Verilog A modules and mixed Verilog A and physical model simulations. Verilog A may also be used in an environment for compact model development but primarily it is used to reduce schematics of significant amounts of transistors into efficient maintainable and changeable blocks which can be instantiated on any level of a design.

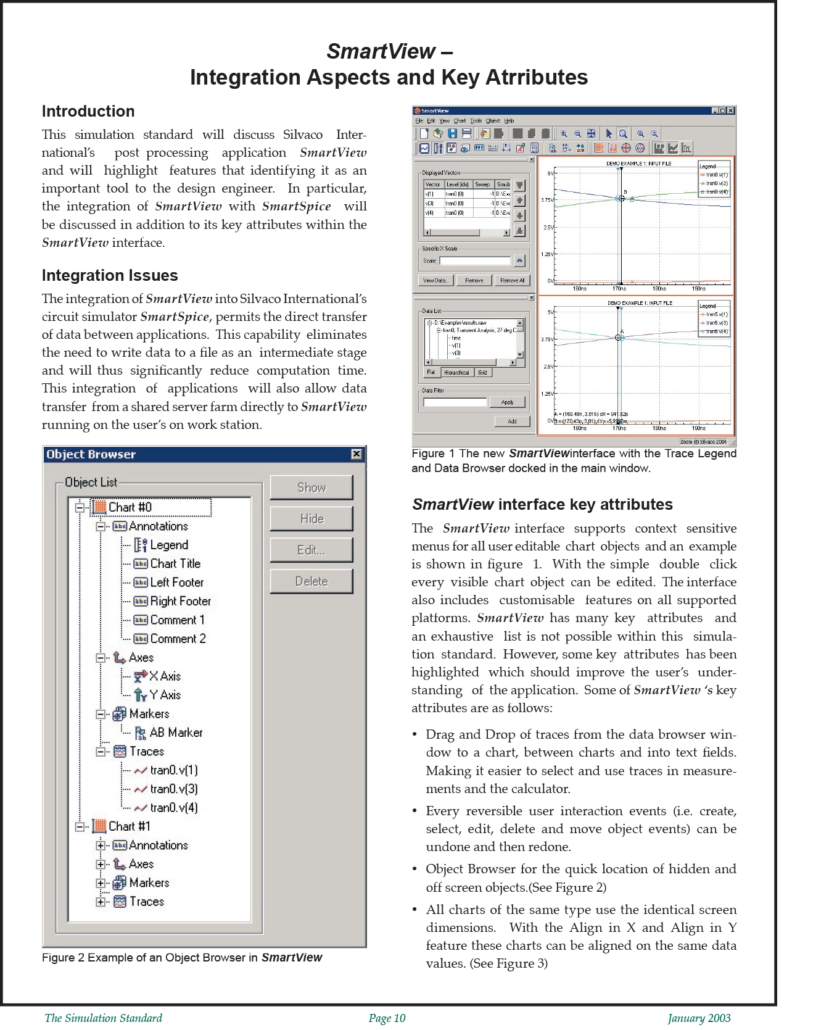

SmartView – Integration Aspects and Key Attributes

This simulation standard will discuss Silvaco International’s post processing application SmartView and will highlight features that identifying it as an important tool to the design engineer. In particular, the integration of SmartView with SmartSpice will be discussed in addition to its key attributes within the SmartView interface.

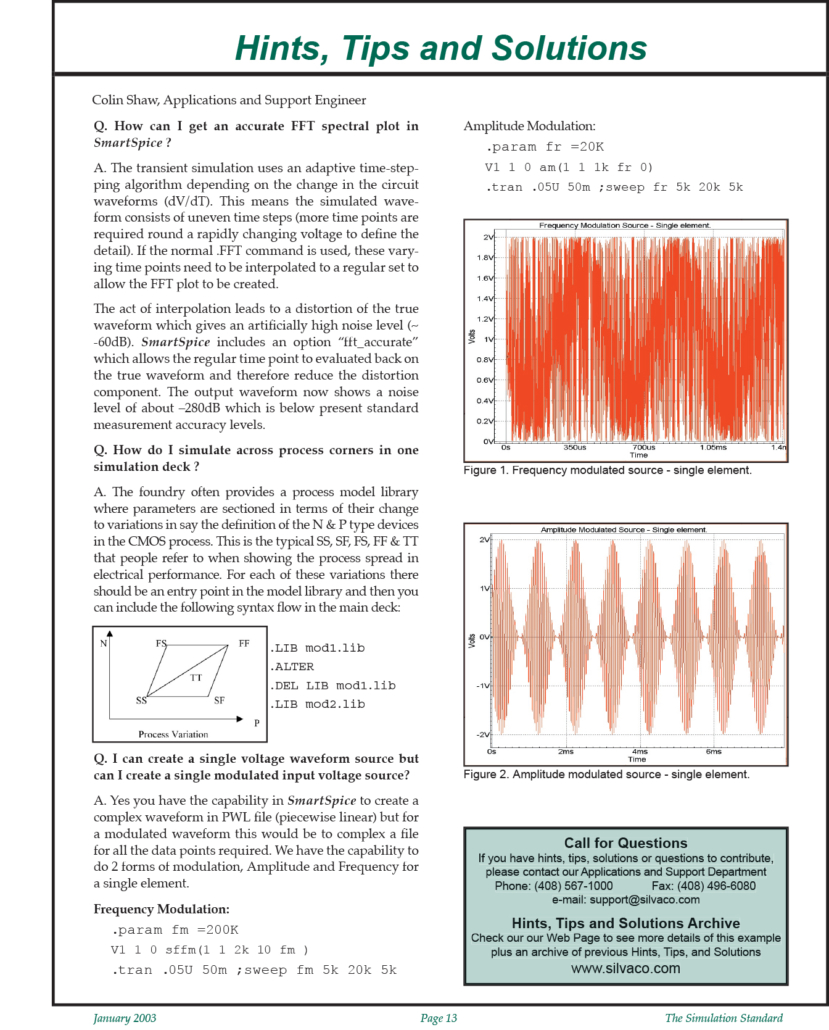

Getting an Accurate FFT Spectral Plot in SmartSpice

The transient simulation uses an adaptive time-stepping algorithm depending on the change in the circuit waveforms (dV/dT). This means the simulated waveform consists of uneven time steps (more time points are required round a rapidly changing voltage to define the detail). If the normal .FFT command is used, these varying time points need to be interpolated to a regular set to allow the FFT plot to be created.

Real-time DRC Verification by DRC Guard

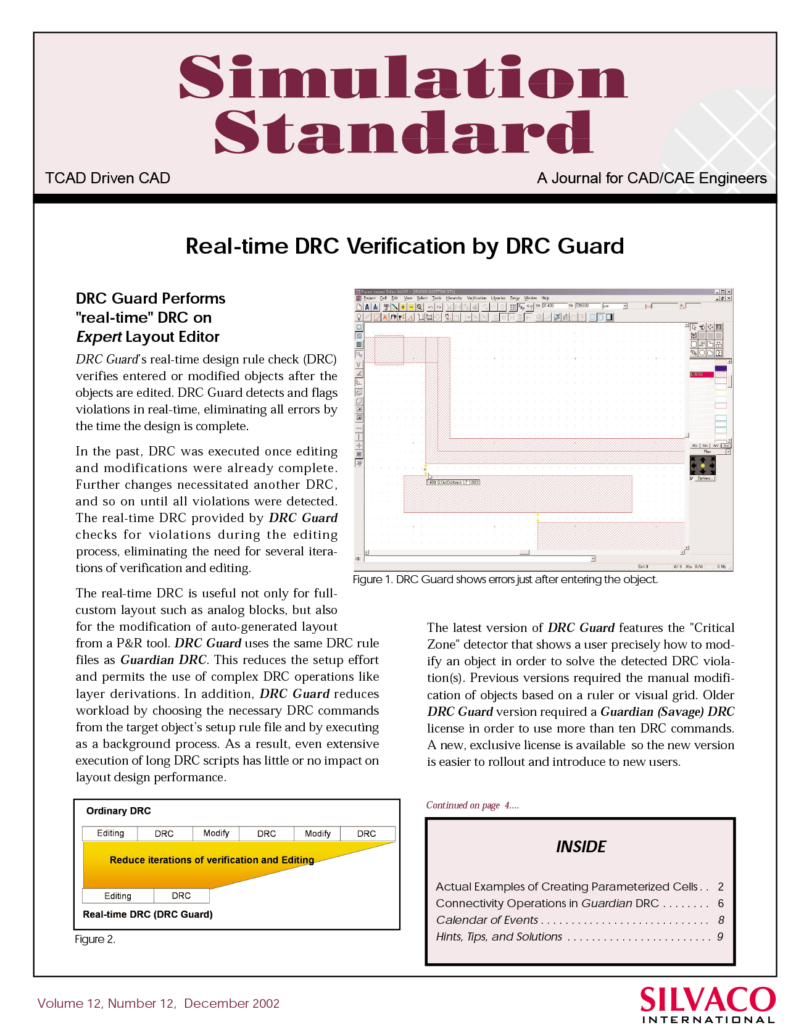

DRC Guard Performs "real-time" DRC on Expert Layout Editor. DRC Guard’s real-time design rule check (DRC) verifies entered or modified objects after the objects are edited. DRC Guard detects and flags violations in real-time, eliminating all errors by the time the design is complete.

Actual Examples of Creating Parameterized Cells

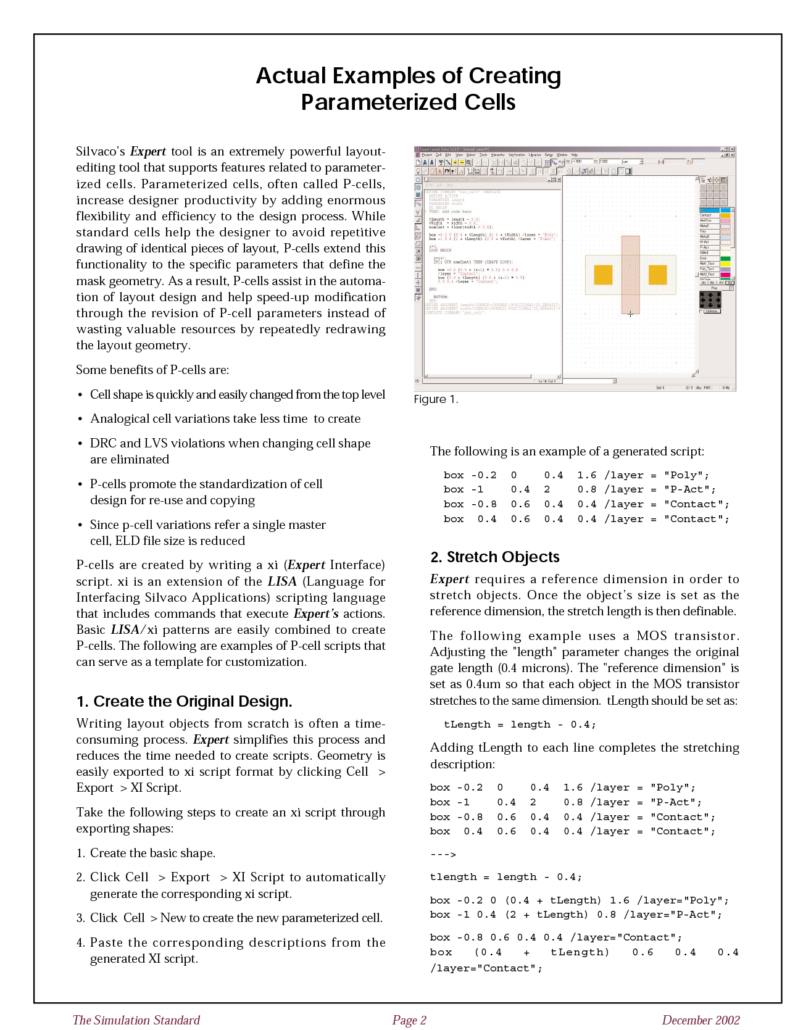

Silvaco’s Expert tool is an extremely powerful layout-editing tool that supports features related to parameterized cells. Parameterized cells, often called P-cells, increase designer productivity by adding enormous flexibility and efficiency to the design process. While standard cells help the designer to avoid repetitive drawing of identical pieces of layout, P-cells extend this functionality to the specific parameters that define the mask geometry. As a result, P-cells assist in the automation of layout design and help speed-up modification through the revision of P-cell parameters instead of wasting valuable resources by repeatedly redrawing the layout geometry.