Simulation Standard Technical Journal

A Journal for Process and Device Engineers

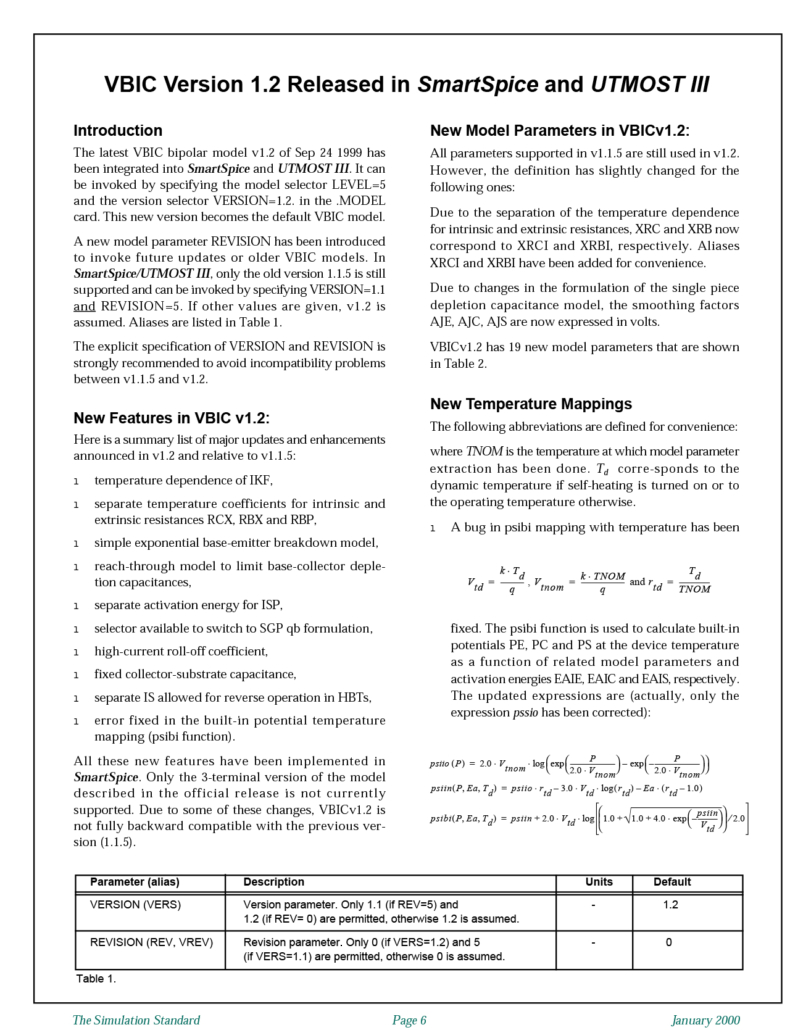

VBIC Version 1.2 Released in SmartSpice and UTMOST III

The latest VBIC bipolar model v1.2 of Sep 24 1999 has been integrated into SmartSpice and UTMOST III. It can be invoked by specifying the model selector LEVEL=5 and the version selector VERSION=1.2. in the .MODEL card. This new version becomes the default VBIC model.

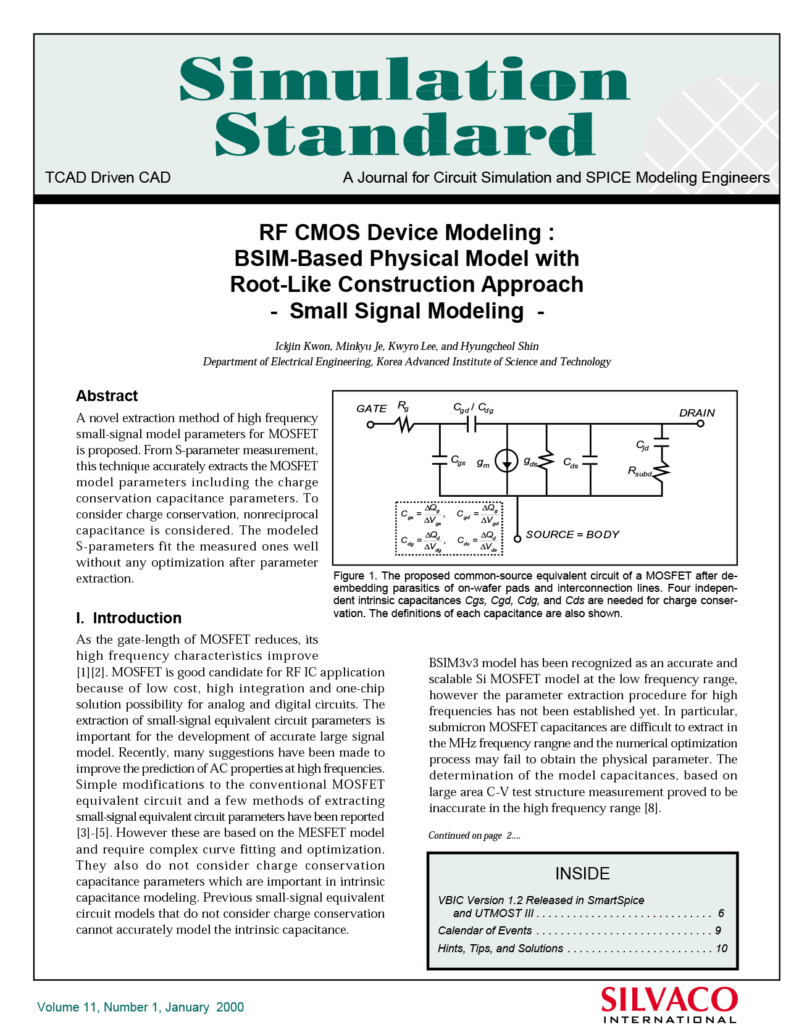

RF CMOS Device Modeling: BSIM-Based Physical Model with Root-Like Construction Approach – Small Signal Modeling

A novel extraction method of high frequency small-signal model parameters for MOSFET is proposed. From S-parameter measurement, this technique accurately extracts the MOSFET model parameters including the charge conservation capacitance parameters. To consider charge conservation, nonreciprocal capacitance is considered. The modeled S-parameters fit the measured ones well without any optimization after parameter extraction.

Hints & Tips December 1999

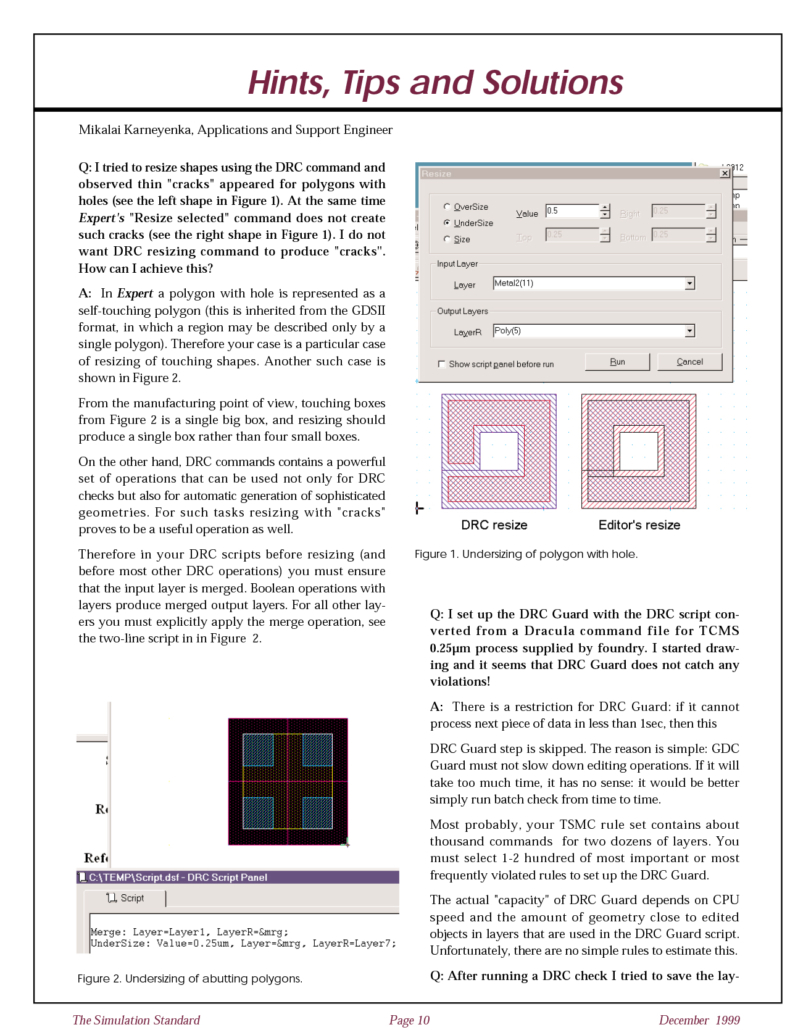

Q: I tried to resize shapes using the DRC command and observed thin "cracks" appeared for polygons with holes (see the left shape in Figure 1). At the same time Expert's "Resize selected" command does not create such cracks (see the right shape in Figure 1). I do not want DRC resizing command to produce "cracks". How can I achieve this?

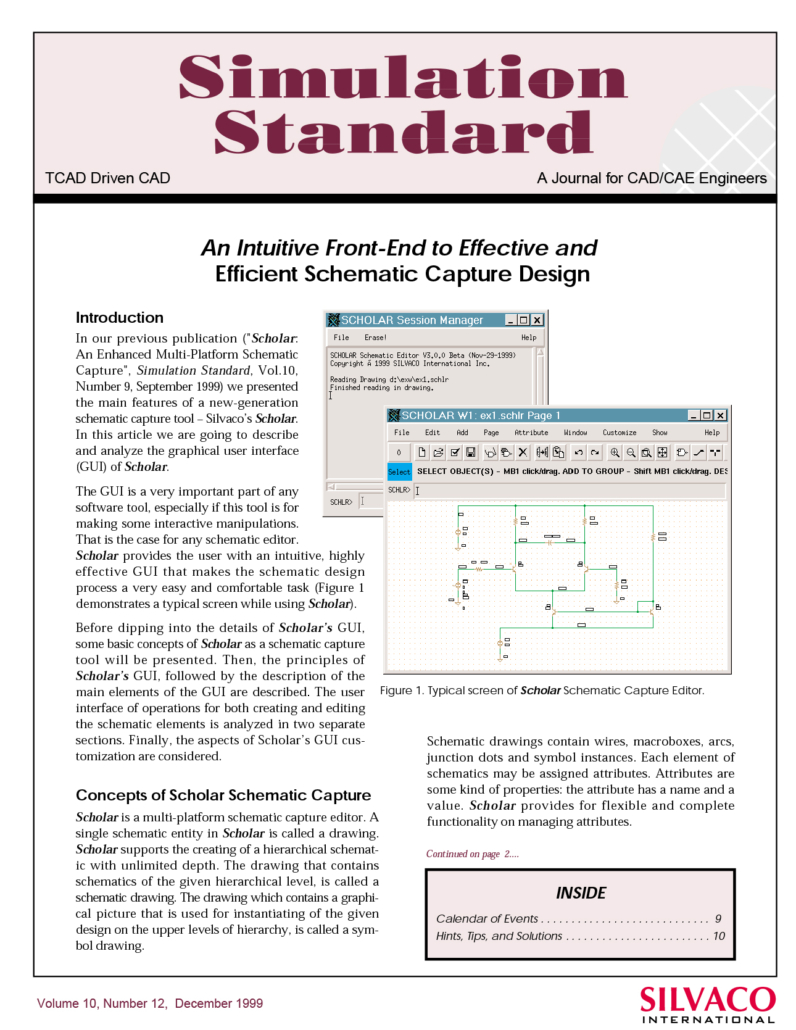

An Intuitive Front-End to Effective and Efficient Schematic Capture Design

In our previous publication ("Scholar: An Enhanced Multi-Platform Schematic Capture", Simulation Standard, Vol.10, Number 9, September 1999) we presented the main features of a new-generation schematic capture tool - Silvaco's Scholar. In this article we are going to describe and analyze the graphical user interface (GUI) of Scholar.

Hints & Tips November 1999

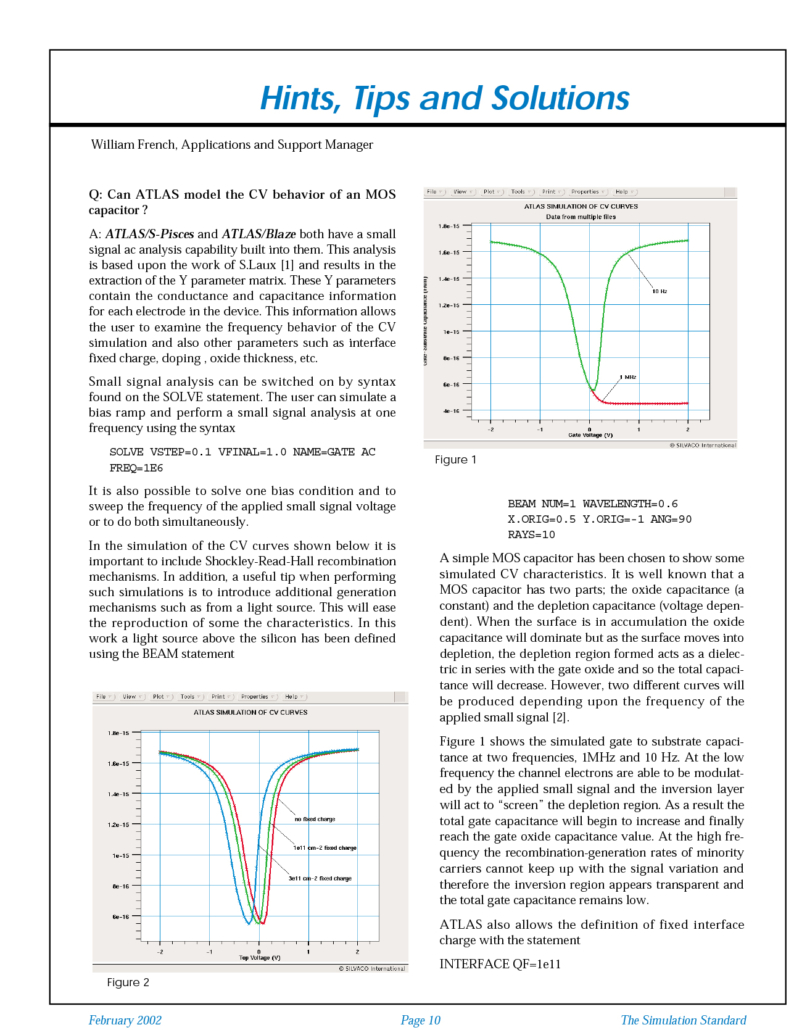

A: ATLAS/S-Pisces and ATLAS/Blaze both have a small signal ac analysis capability built into them. This analysis is based upon the work of S.Laux [1] and results in the extraction of the Y parameter matrix. These Y parameters contain the conductance and capacitance information for each electrode in the device. This information allows the user to examine the frequency behavior of the CV simulation and also other parameters such as interface fixed charge, doping , oxide thickness, etc.

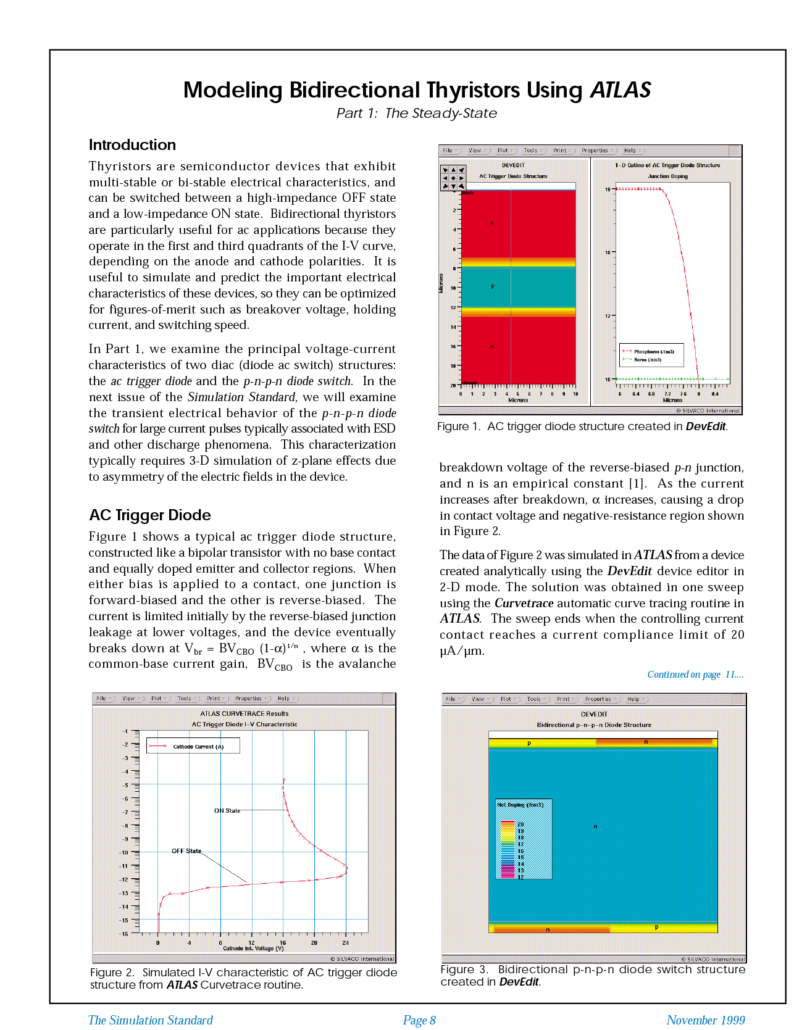

Modeling Bidirectional Thyristors Using ATLAS

Thyristors are semiconductor devices that exhibit multi-stable or bi-stable electrical characteristics, and can be switched between a high-impedance OFF state and a low-impedance ON state. Bidirectional thyristors are particularly useful for ac applications because they operate in the first and third quadrants of the I-V curve, depending on the anode and cathode polarities. It is useful to simulate and predict the important electrical characteristics of these devices, so they can be optimized for figures-of-merit such as breakover voltage, holding current, and switching speed.