Simulation Standard Technical Journal

A Journal for Process and Device Engineers

Using The Statistical Sampling Feature in the BCA Monte Carlo Implant Simulator

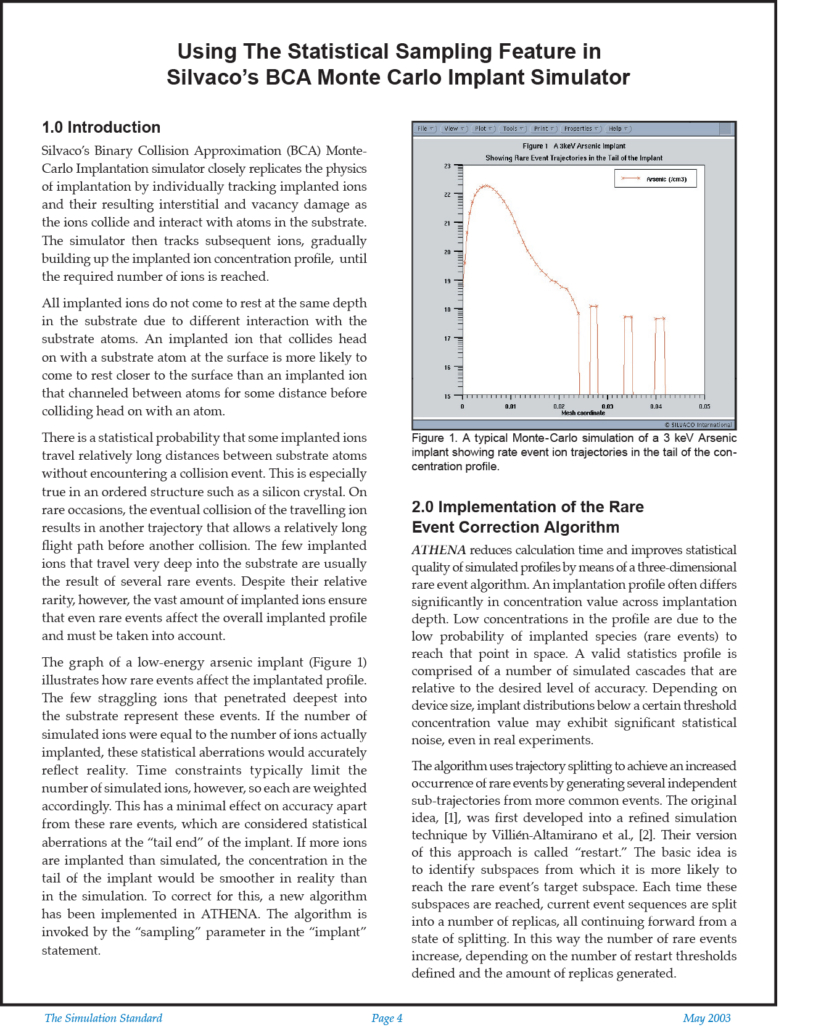

Silvaco’s Binary Collision Approximation (BCA) Monte- Carlo Implantation simulator closely replicates the physics of implantation by individually tracking implanted ions and their resulting interstitial and vacancy damage as the ions collide and interact with atoms in the substrate. The simulator then tracks subsequent ions, gradually building up the implanted ion concentration profile, until the required number of ions is reached.

A Comparison Between Classical Full Chip Extraction and Field Solver Parasitic Extraction

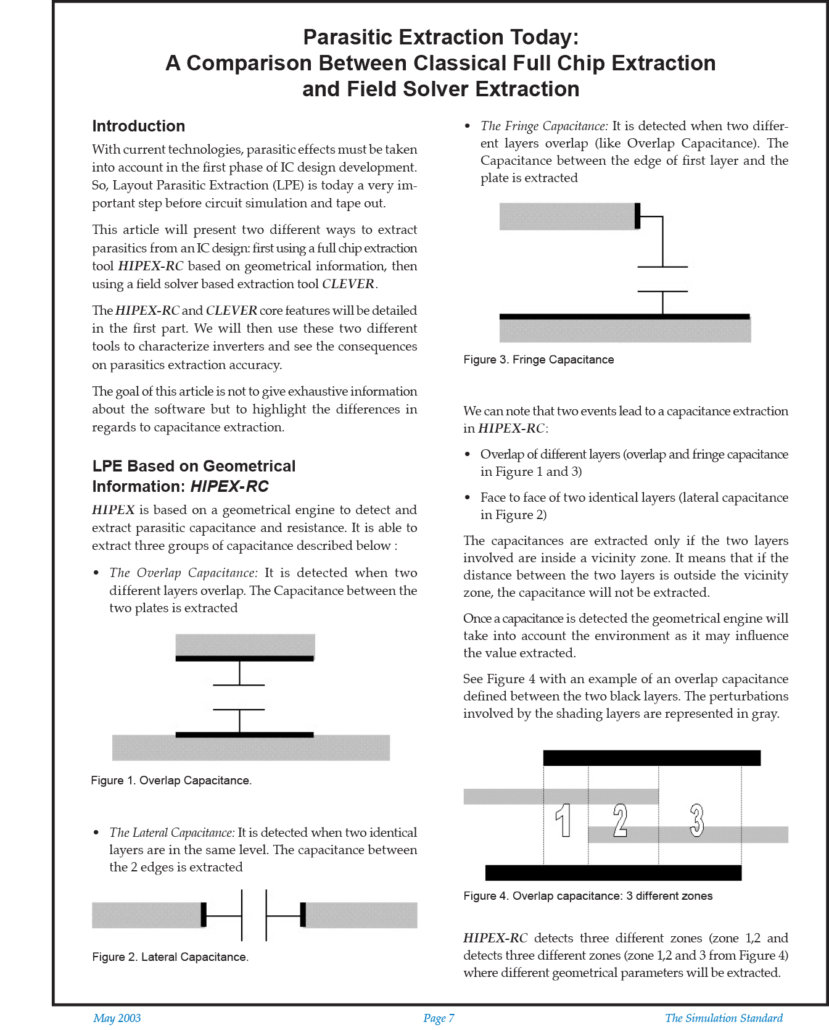

This article will present two different ways to extract parasitics from an IC design: first using a full chip extraction tool HIPEX-RC based on geometrical information, then using a field solver based extraction tool CLEVER.

ATLAS Simulation of an SEU Event in 2D

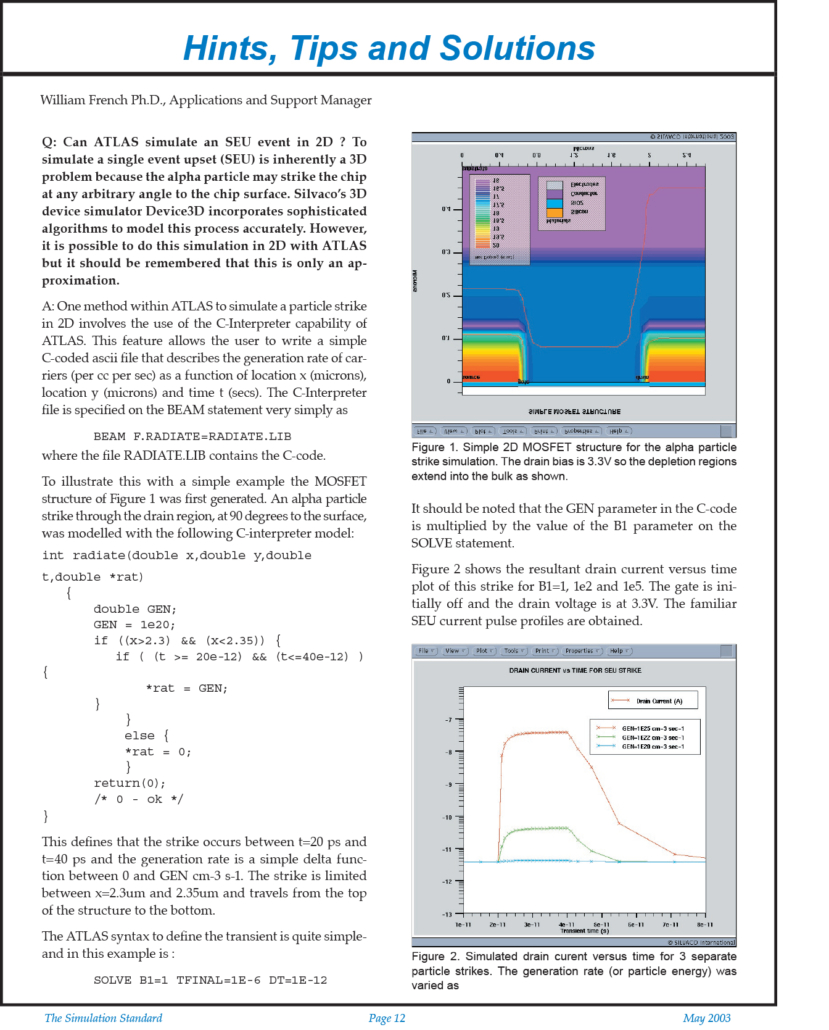

Q: Can ATLAS simulate an SEU event in 2D? To simulate a single event upset (SEU) is inherently a 3D problem because the alpha particle may strike the chip at any arbitrary angle to the chip surface. Silvaco’s 3D device simulator Device3D incorporates sophisticated algorithms to model this process accurately. However, it is possible to do this simulation in 2D with ATLAS but it should be remembered that this is only an approximation.

RPI VCSEL Model Released in SmartSpice

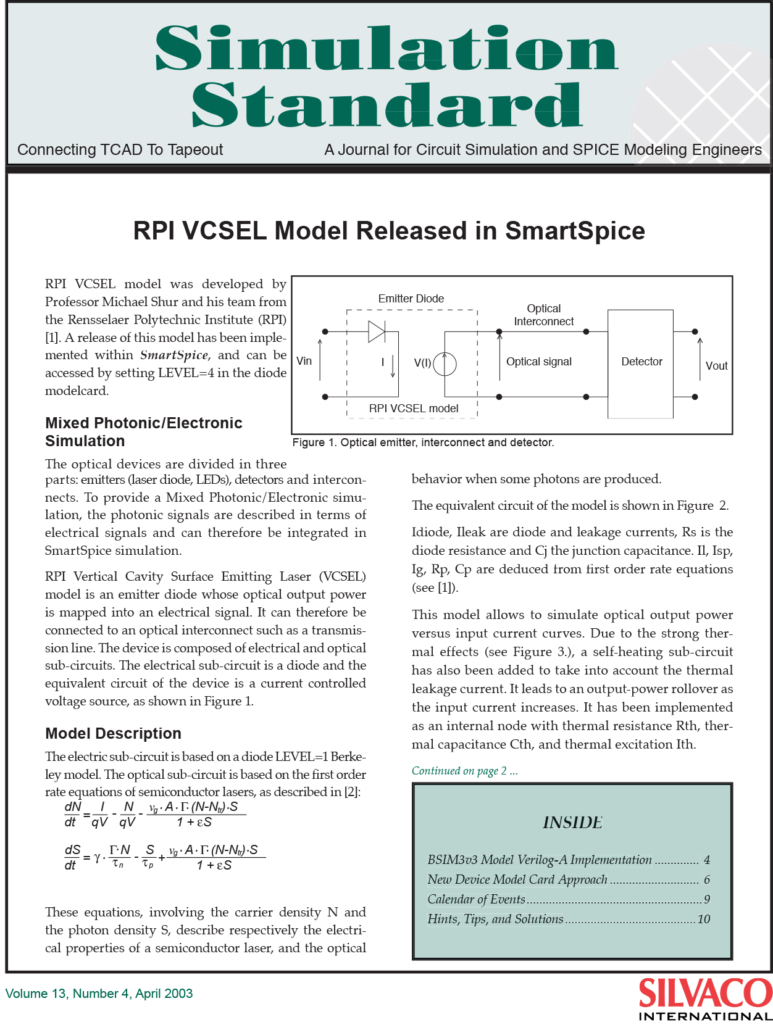

RPI VCSEL model was developed by Professor Michael Shur and his team from the Rensselaer Polytechnic Institute (RPI) [1]. A release of this model has been implemented within SmartSpice, and can be accessed by setting LEVEL=4 in the diode modelcard.

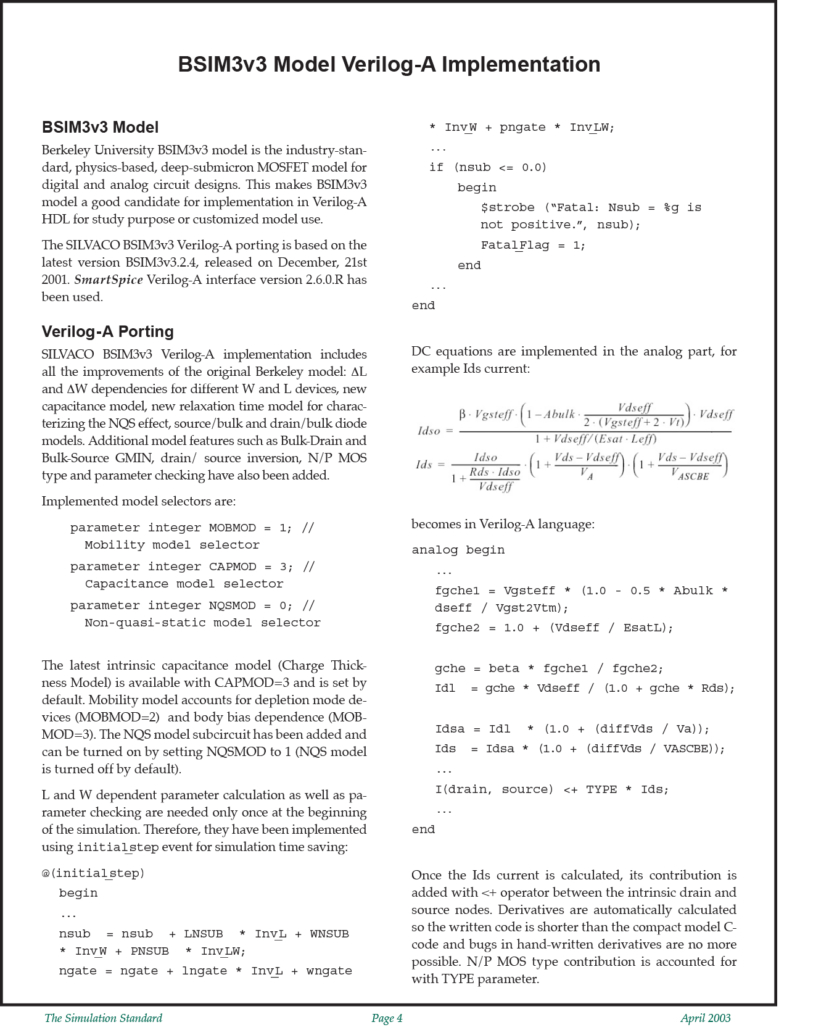

BSIM3v3 Model Verilog-A Implementation

Berkeley University BSIM3v3 model is the industry-standard, physics-based, deep-submicron MOSFET model for digital and analog circuit designs. This makes BSIM3v3 model a good candidate for implementation in Verilog-A HDL for study purpose or customized model use.

New Device Model Card Approach

Normally a single active device model is extracted to cover a range of device geometries and temperature. Sometimes this single scalable model is not sufficient to describe all the changes in output characteristics over the range of geometry and temperature required. The total range of geometry and temperature is then broken up into regions and a model produced for each of these sub-sets of devices. This is the basis of a binned model and can lead to discontinuities at the bin boundaries as the model card is changed. To get round this problem SmartSpice has introduced a new functionality to allow the user to go back towards a single scalable model card via the use of a function rather than a single parameter value.