Simulation Standard

Silvaco面向半导体工艺和器件仿真工程师推出的技术刊物

Modeling and Parameter Extraction Technique for HV MOS Devices with BSIM3v3

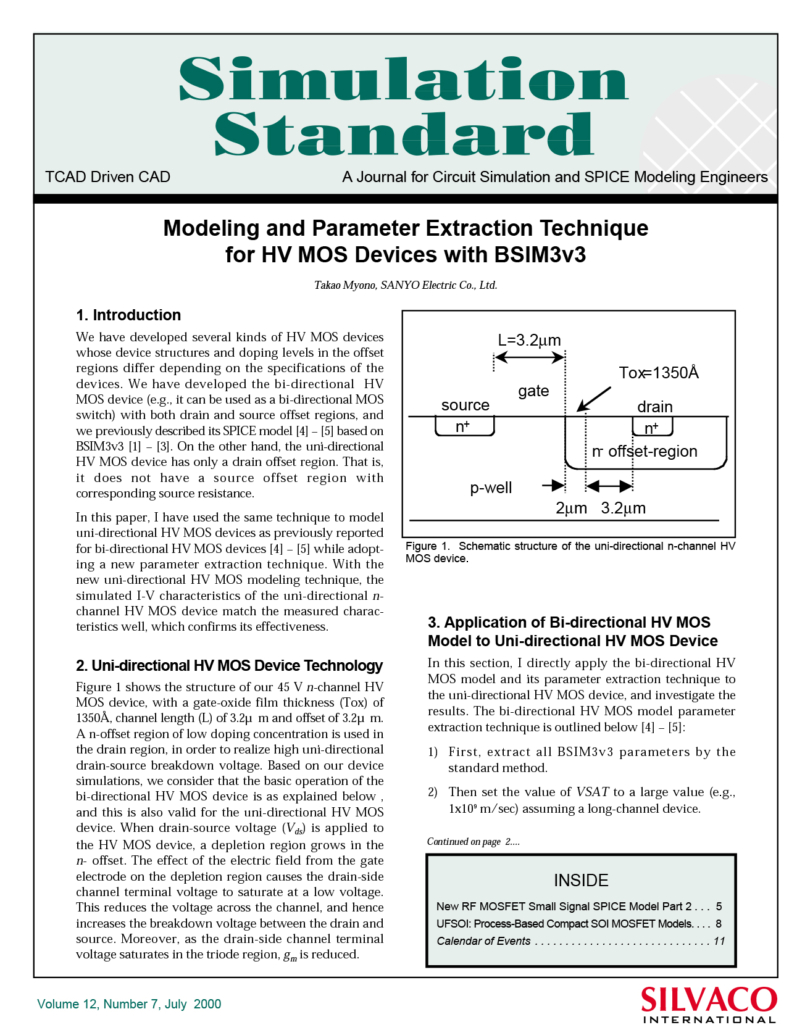

In this paper, I have used the same technique to model uni-directional HV MOS devices as previously reported for bi-directional HV MOS devices [4] -[5] while adopting a new parameter extraction technique. With the new uni-directional HV MOS modeling technique, the simulated I-V characteristics of the uni-directional n-channel HV MOS device match the measured characteristics well, which confirms its effectiveness.

New RF MOSFET Small Signal SPICE Model – Part 2

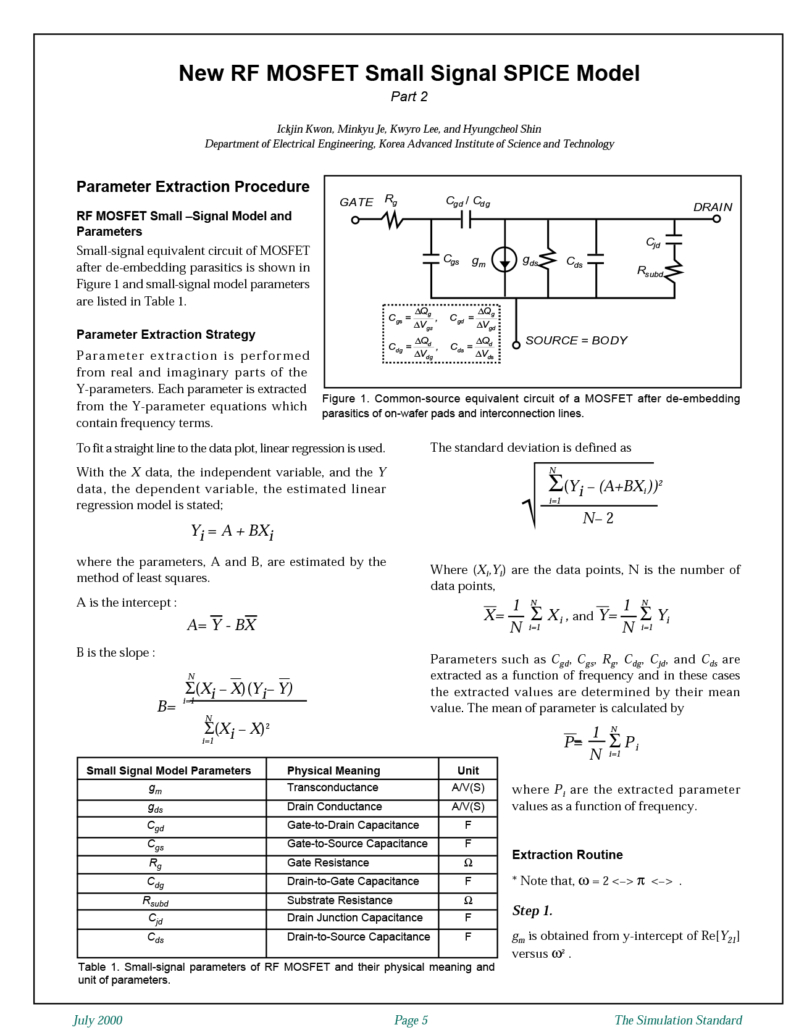

RF MOSFET Small - Signal Model and Parameters

Small-signal equivalent circuit of MOSFET after de-embedding parasitics is shown in Figure 1 and small-signal model parameters are listed in Table 1.

Parameter extraction is performed from real and imaginary parts of the Y-parameters. Each parameter is extracted from the Y-parameter equations which contain frequency terms.

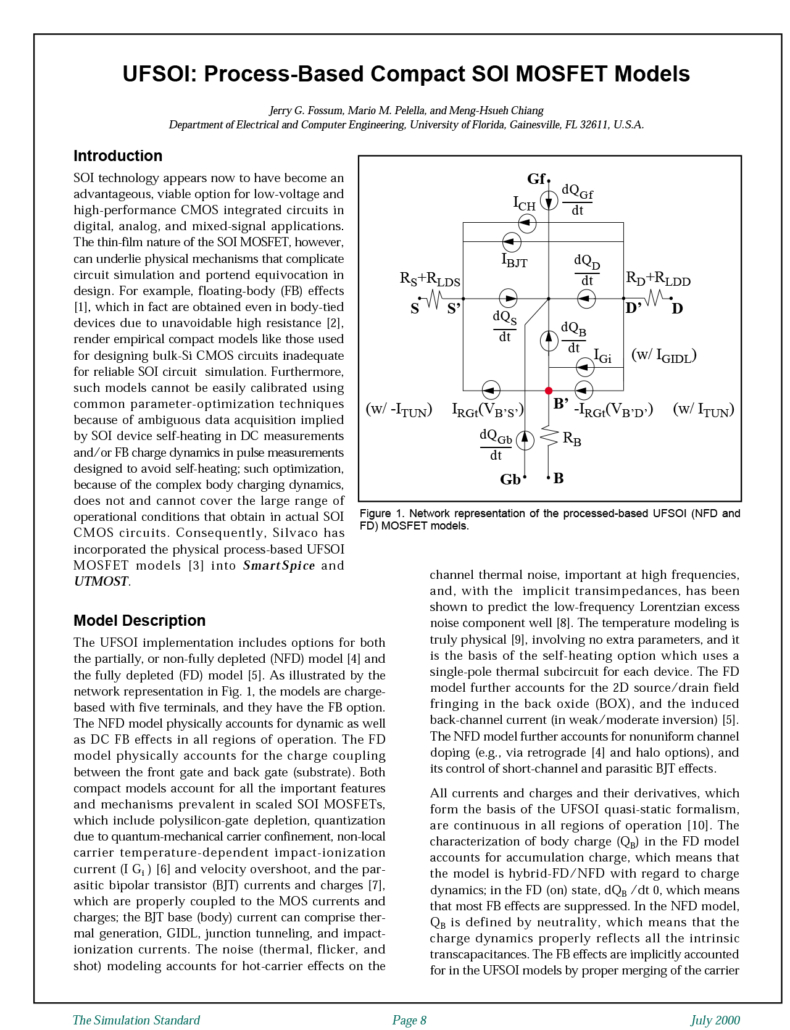

UFSOI: Process-Based Compact SOI MOSFET Models

SOI technology appears now to have become an advantageous, viable option for low-voltage and high-performance CMOS integrated circuits in digital, analog, and mixed-signal applications. The thin-film nature of the SOI MOSFET, however, can underlie physical mechanisms that complicate circuit simulation and portend equivocation in design. Consequently, Silvaco has incorporated the physical process-based UFSOI MOSFET models into SmartSpice and Utmost.

Hints, Tips, and Solutions June 2000

Q: To simplify netlist extraction, I specify one kind of diffusion resistors in my layout by means of a special resistor definition layer. To my surprise, the extracted value for one such resistor always exactly twice the value I expected, no matter how I stretch this resistor.

Parametric-Cells Implementation in Expert

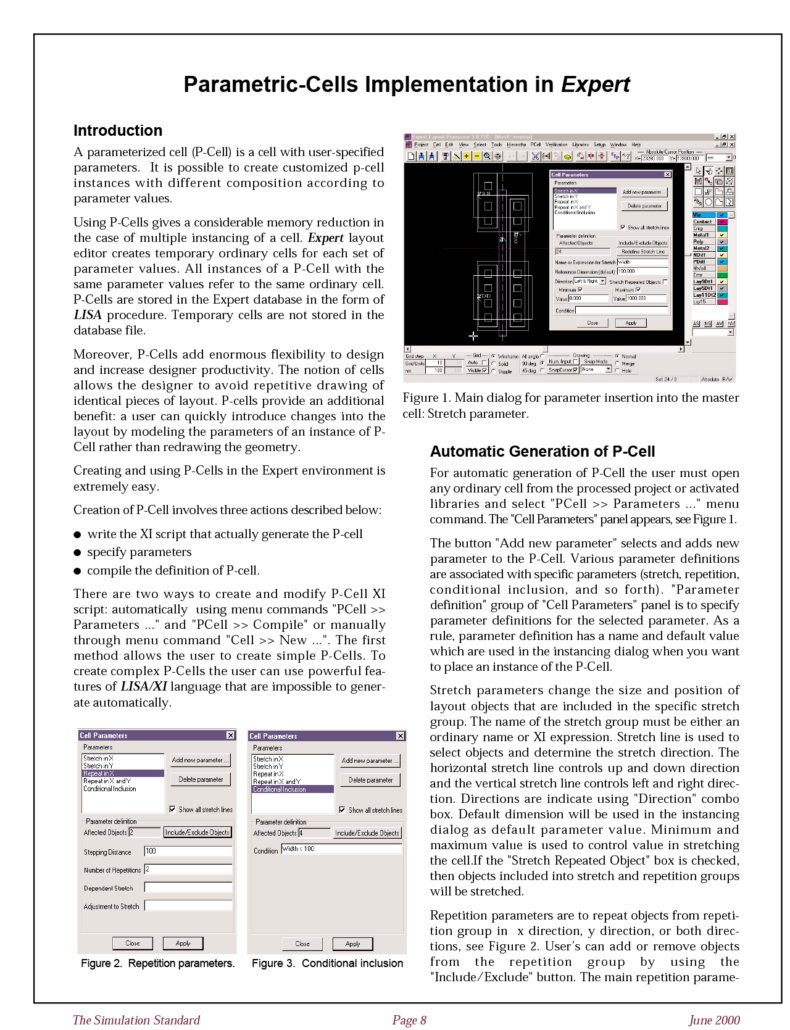

A parameterized cell (P-Cell) is a cell with user-specified parameters. It is possible to create customized p-cell instances with different composition according to parameter values. Using P-Cells gives a considerable memory reduction in the case of multiple instancing of a cell.

Dragon DRC: Performance Improvement Techniques

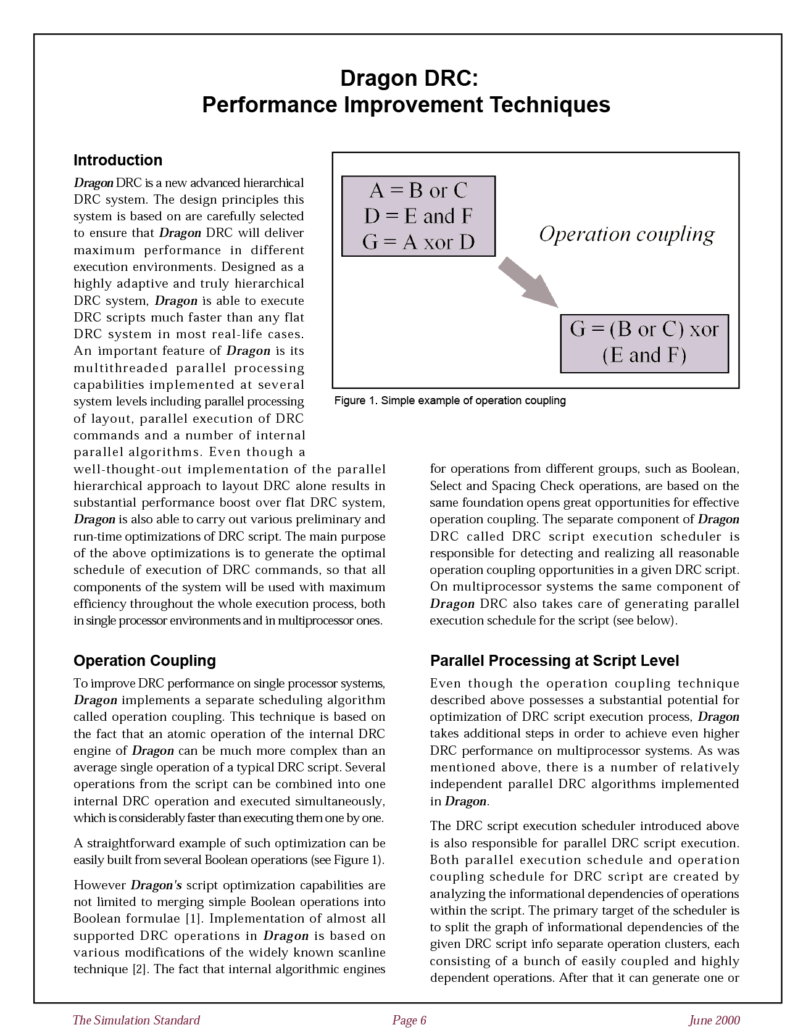

Dragon DRC is a new advanced hierarchical DRC system. The design principles this system is based on are carefully selected to ensure that Dragon DRC will deliver maximum performance in different execution environments. Designed as a highly adaptive and truly hierarchical DRC system, Dragon is able to execute DRC scripts much faster than any flat DRC system in most real-life cases.