Simulation Standard

Silvaco面向半导体工艺和器件仿真工程师推出的技术刊物

A New Surface-Potentials Based MOSFET Model: HiSIM

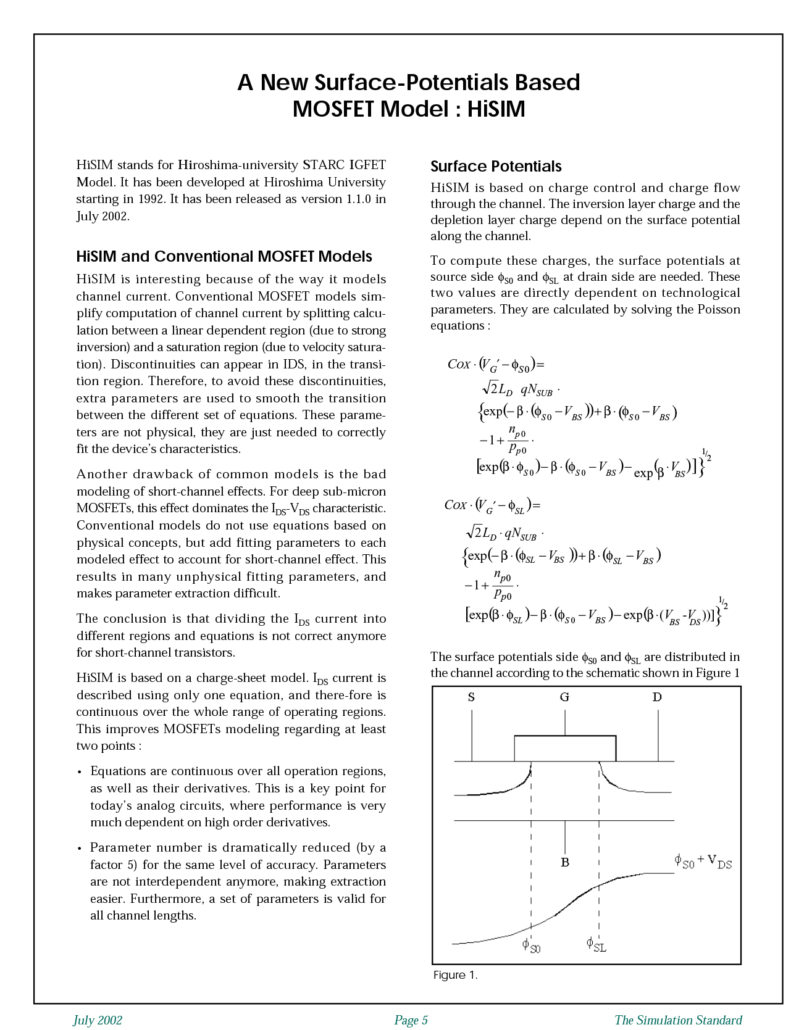

HiSIM is based on a charge-sheet model. IDS current is described using only one equation, and there-fore is continuous over the whole range of operating regions. This improves MOSFETs modeling regarding at least two points. Equations are continuous over all operation regions, as well as their derivatives. This is a key point for today’s analog circuits, where performance is very much dependent on high order derivatives. Parameter number is dramatically reduced (by a factor 5) for the same level of accuracy. Parameters are not interdependent anymore, making extraction easier. Furthermore, a set of parameters is valid for all channel lengths.

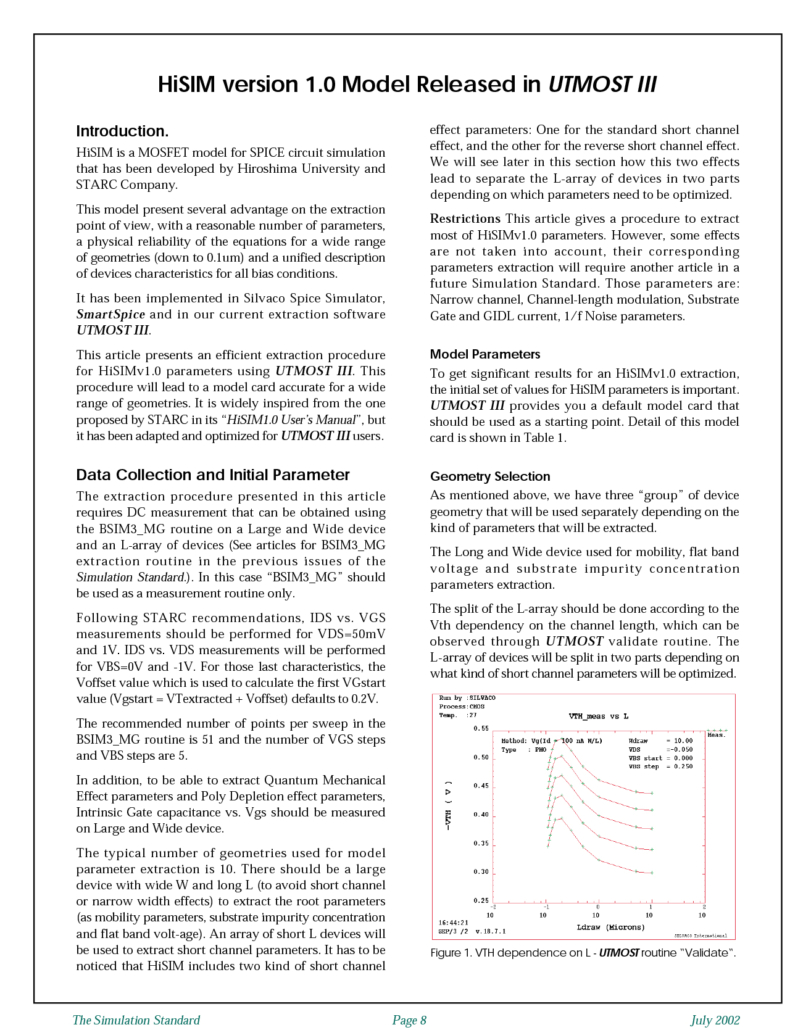

HiSIM Version 1.0 Model Released in UTMOST III

HiSIM is a MOSFET model for SPICE circuit simulation that has been developed by Hiroshima University and STARC Company. This model present several advantage on the extraction point of view, with a reasonable number of parameters, a physical reliability of the equations for a wide range of geometries (down to 0.1um) and a unified description of devices characteristics for all bias conditions. It has been implemented in Silvaco Spice Simulator, SmartSpice and in our current extraction software UTMOST III.

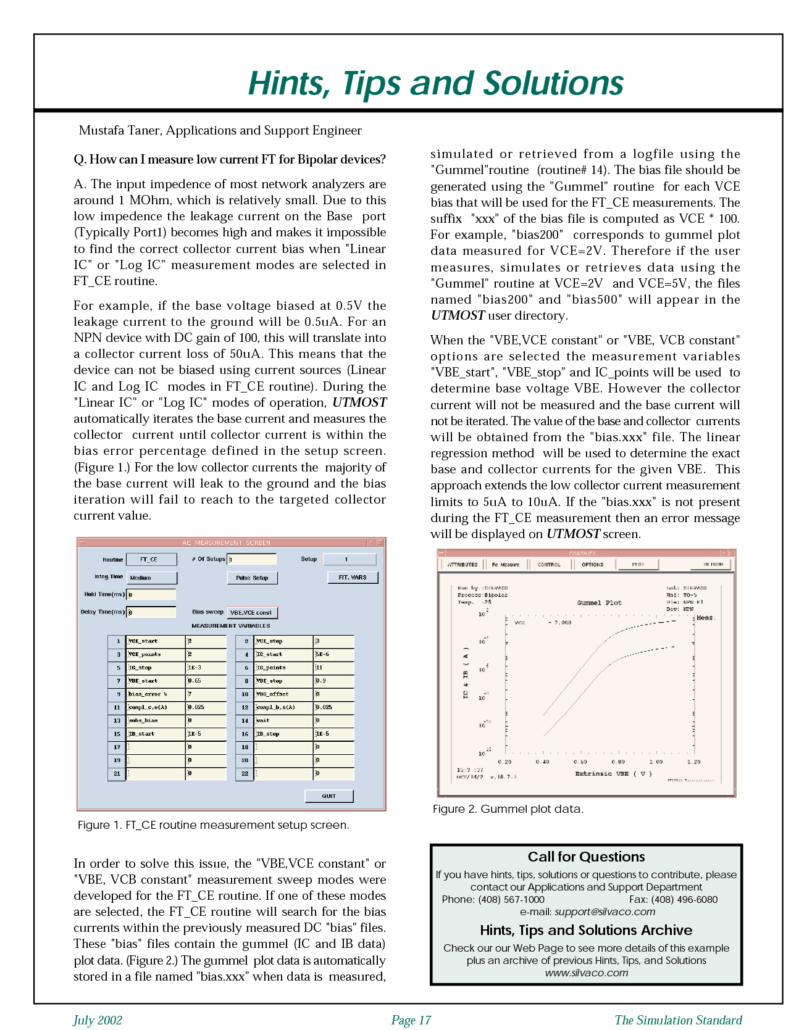

Measure Low Current FT in Bipolar devices

The input impedence of most network analyzers are around 1 MOhm, which is relatively small. Due to this low impedence the leakage current on the Base port (Typically Port1) becames high and makes it impossible to find the correct collector current bias when "Linear IC" or "Log IC" measurement modes are selected in FT_CE routine.

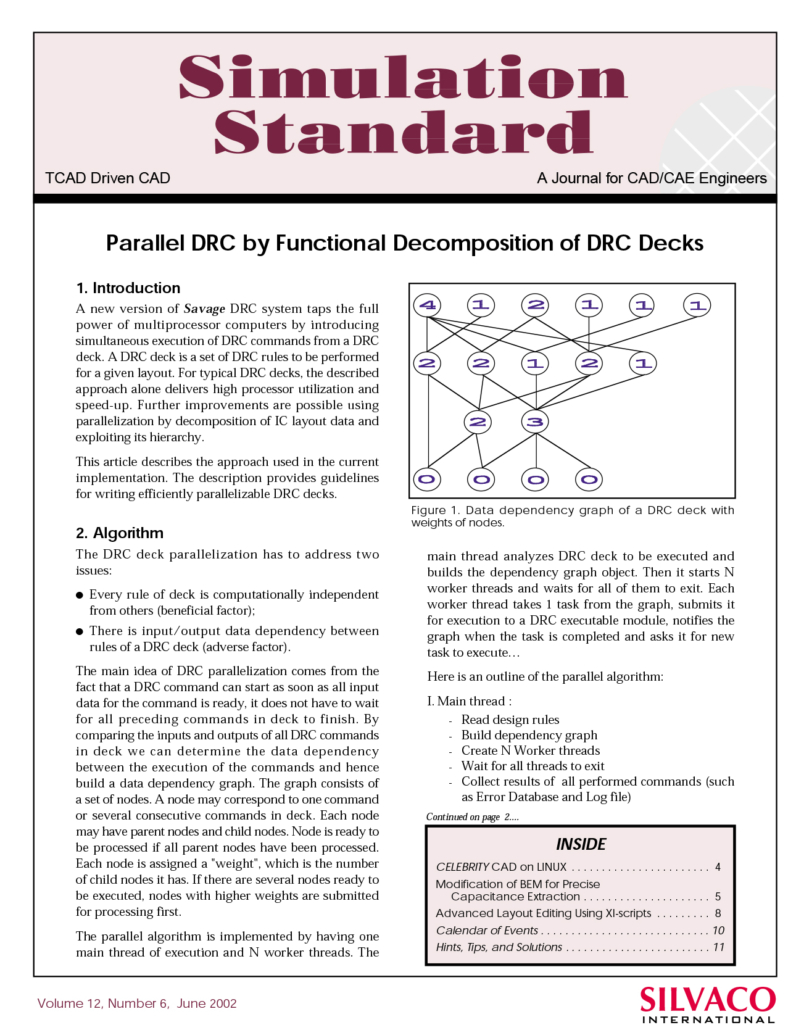

Parallel DRC by Functional Decomposition of DRC Decks

A new version of Savage DRC system taps the full power of multiprocessor computers by introducing simultaneous execution of DRC commands from a DRC deck. A DRC deck is a set of DRC rules to be performed for a given layout. For typical DRC decks, the described approach alone delivers high processor utilization and speed-up. Further improvements are possible using parallelization by decomposition of IC layout data and exploiting its hierarchy.

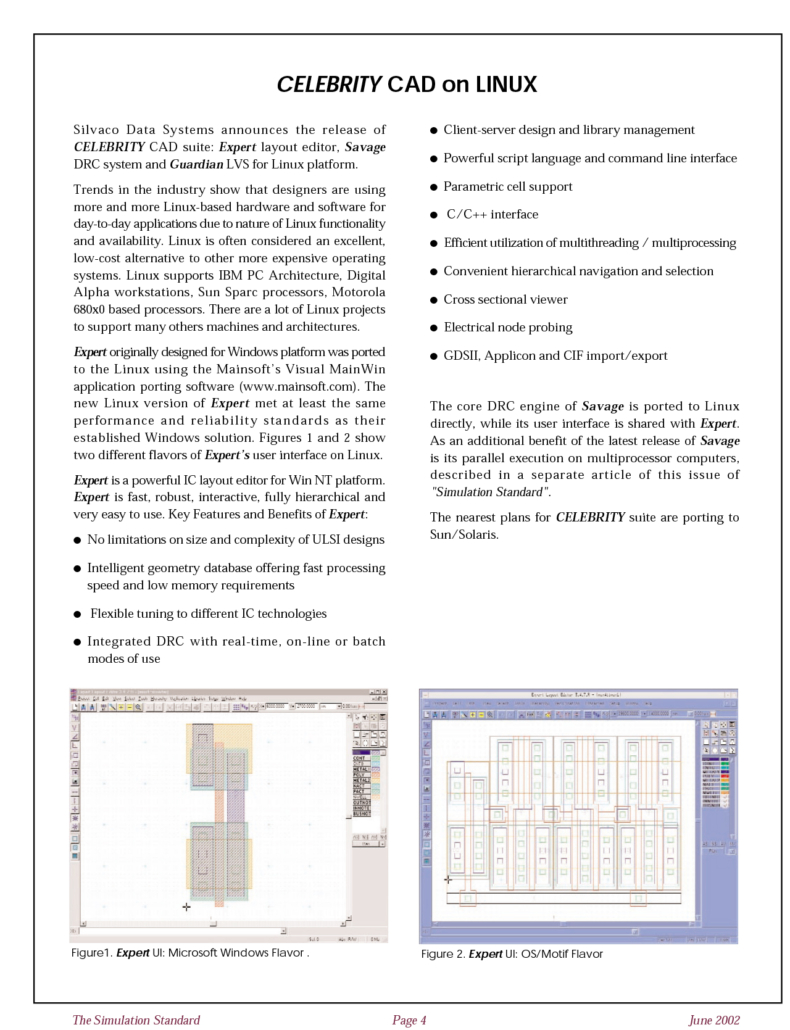

Expert Layout Editor, Savage DRC System and Guardian LVS for Linux Platform

Silvaco Data Systems announces the release of CELEBRITY CAD suite: Expert layout editor, Savage DRC system and Guardian LVS for Linux platform.

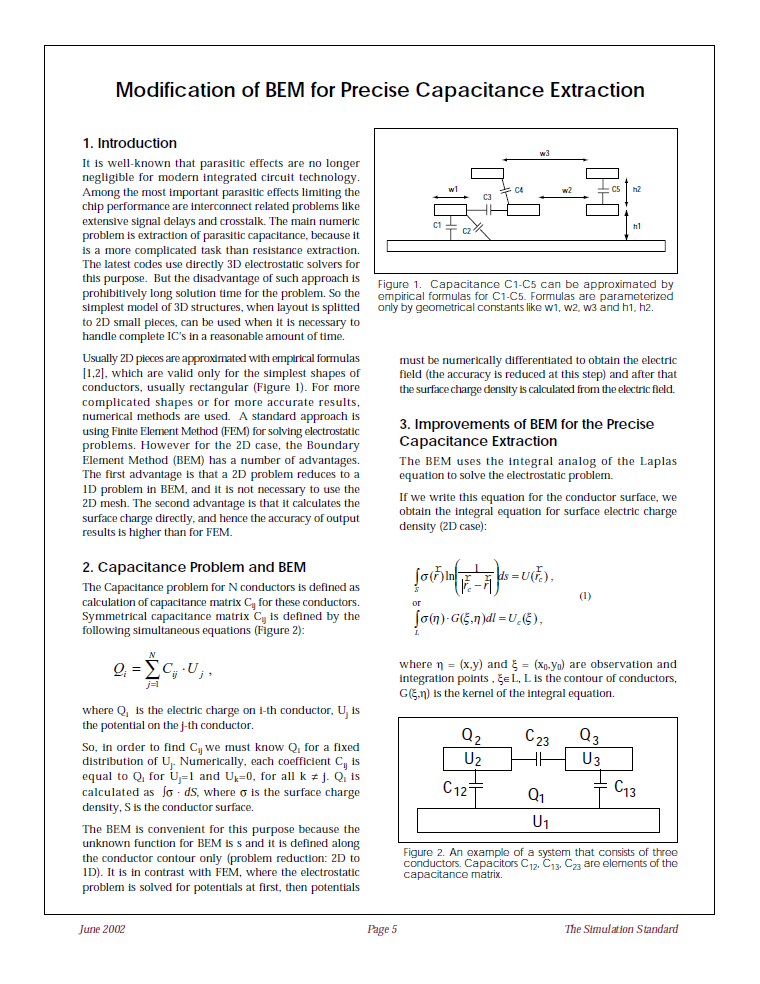

Modification of BEM for Precise Capacitance Extraction

It is well-known that parasitic effects are no longer negligible for modern integrated circuit technology. Among the most important parasitic effects limiting the chip performance are interconnect related problems like extensive signal delays and crosstalk. The main numeric problem is extraction of parasitic capacitance, because it is a more complicated task than resistance extraction. The latest codes use directly 3D electrostatic solvers for this purpose. But the disadvantage of such approach is prohibitively long solution time for the problem. So the simplest model of 3D structures, when layout is splitted to 2D small pieces, can be used when it is necessary to handle complete IC's in a reasonable amount of time.