Simulation Standard

Silvaco面向半导体工艺和器件仿真工程师推出的技术刊物

SmartSpice Tips: Memory Usage, .MODIF & .ALTER, Non-convergence

When you run a long simulation time analysis the evaluated time points are normally all held in memory until the end time is reached. All the data is then written out to the output rawfile. This means a large amount of system memory can be used up and also has to be tracked. If in the input deck the line “.OPTIONS RAWPTS=300 POST” is included then as soon as the maximum number of points is reached given by “RAWPTS=300” then all the vector data is saved to the raw data output file and the memory is free to be re-used. In this way the output rawfile is incrementally increased in size every time this limit is reached. The memory required by the simulation run is therefore reduced, and with less memory to manage, the simulation is run faster. This is particularly useful on the PC platform where some of the memory is required for the operating system and RAM size is less than 1GB.

Guardian-Net Netlist Extractor: An Example of Specific Device Extraction Using XI-Scripts

Guardian LVS from Silvaco is an efficient, reliable, and diverse package that brings the benefit of high-speed verification to PC-based test environments. Guardian netlist extractor, included with the Guardian suite, is a dynamic module that supports the high-speed extraction of a variety of devices, including MOS transistors, resistors, capacitors, and other standard devices.

Complex Parallel-Series Reduction

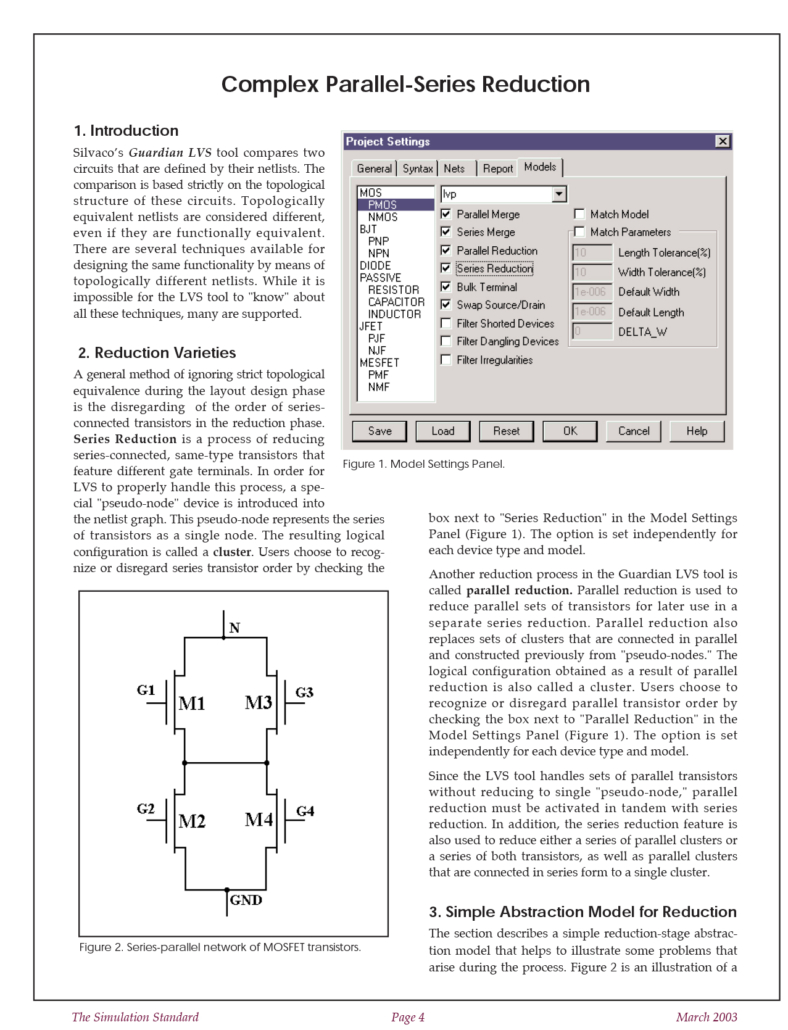

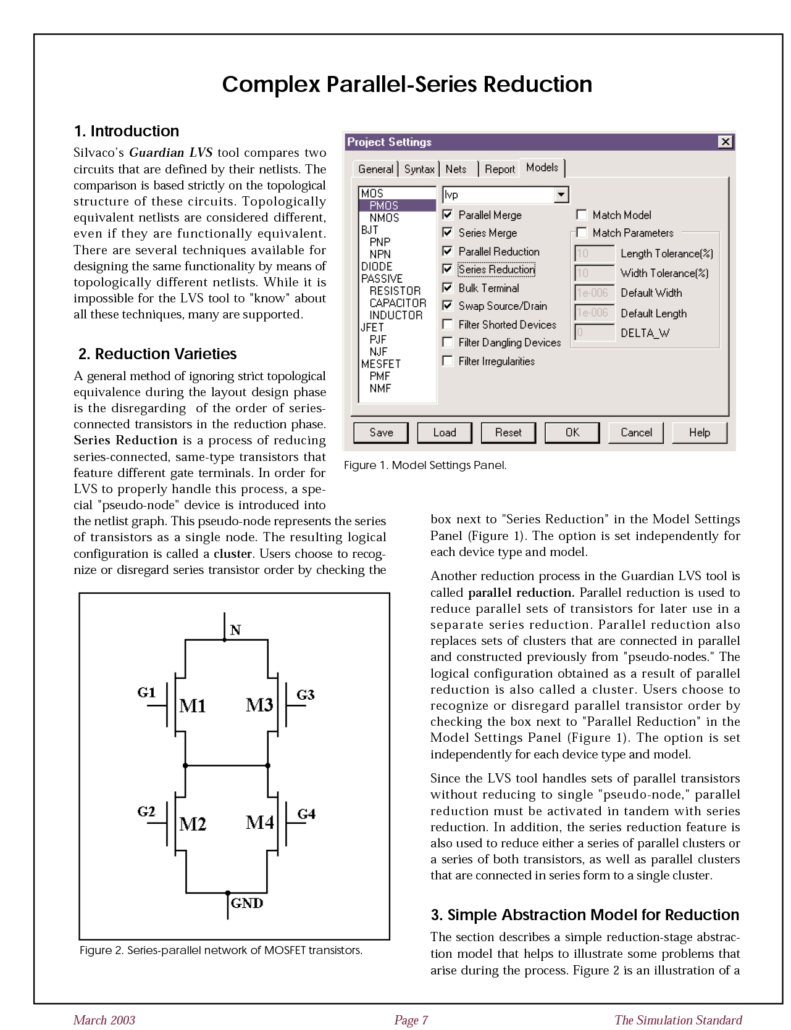

Silvaco’s Guardian LVS tool compares two circuits that are defined by their netlists. The comparison is based strictly on the topological structure of these circuits. Topologically equivalent netlists are considered different, even if they are functionally equivalent. There are several techniques available for designing the same functionality by means of topologically different netlists. While it is impossible for the LVS tool to "know" about all these techniques, many are supported.

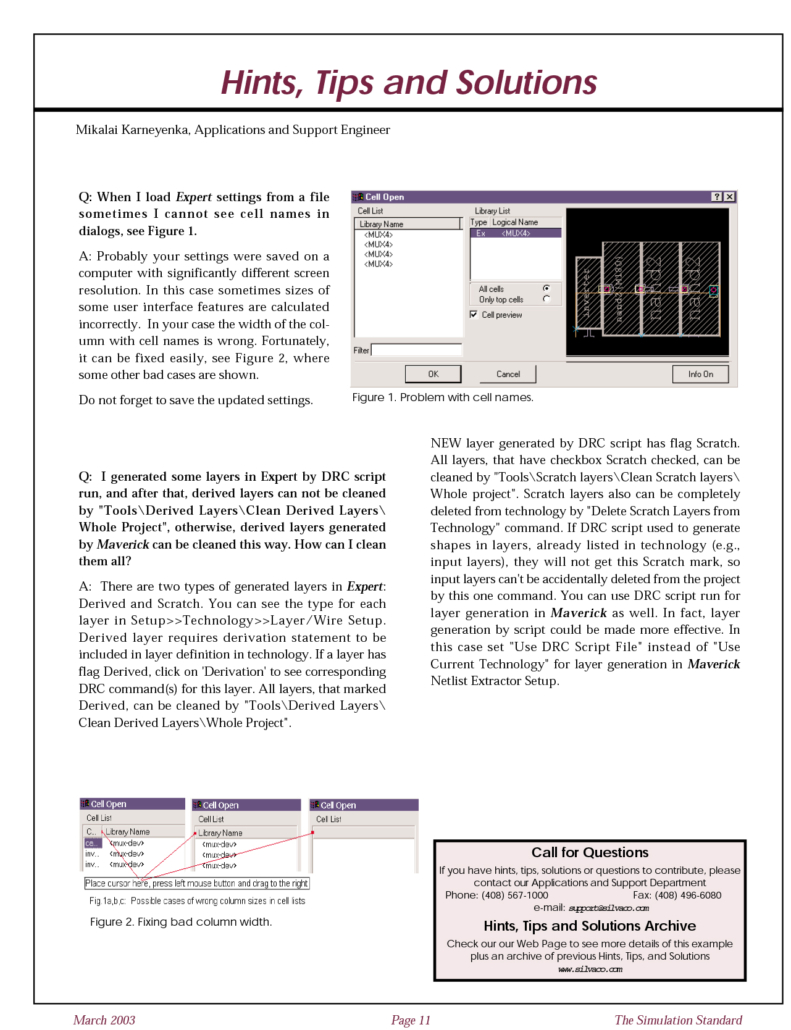

Expert Editor Settings and Layer Cleaning

I generated some layers in Expert by DRC script run, and after that, derived layers can not be cleaned by "Tools\Derived Layers\Clean Derived Layers\ Whole Project", otherwise, derived layers generated by Maverick can be cleaned this way. How can I clean them all?

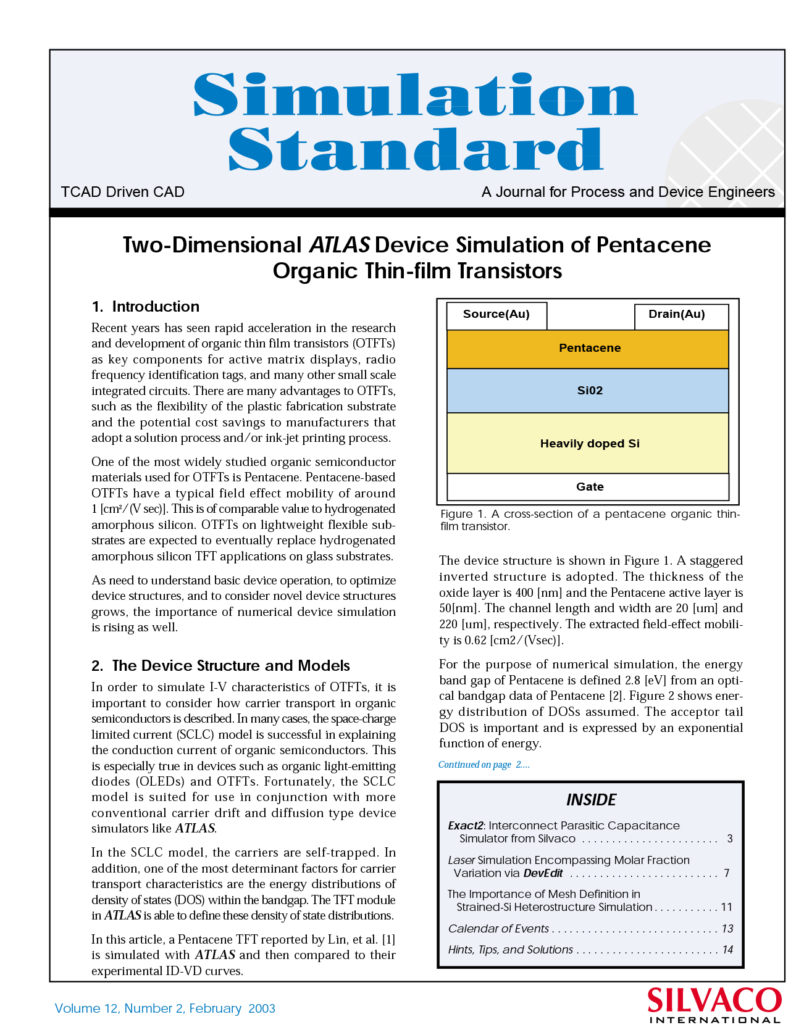

Two-Dimensional ATLAS Device Simulation of Pentacene Organic Thin-film Transistors

Recent years has seen rapid acceleration in the research and development of organic thin film transistors (OTFTs) as key components for active matrix displays, radio frequency identification tags, and many other small scale integrated circuits. There are many advantages to OTFTs, such as the flexibility of the plastic fabrication substrate and the potential cost savings to manufacturers that adopt a solution process and/or ink-jet printing process.

Exact2: Interconnect Parasitic Capacitance Simulator

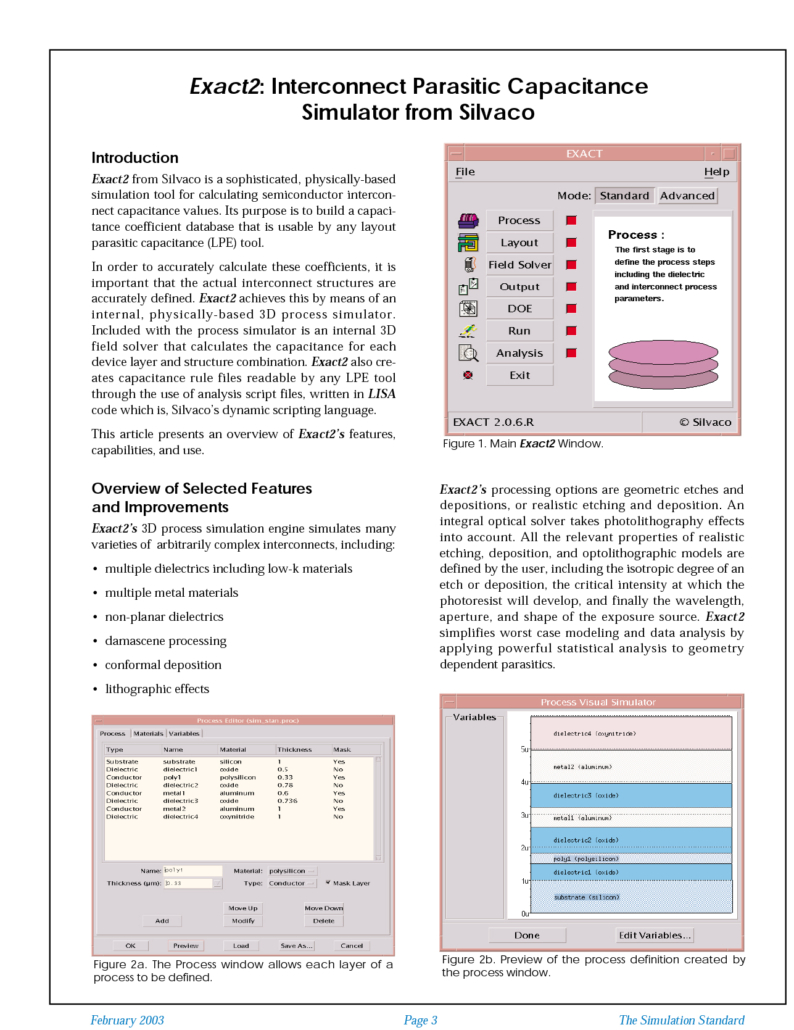

Exact2 from Silvaco is a sophisticated, physically-based simulation tool for calculating semiconductor interconnect capacitance values. Its purpose is to build a capacitance coefficient database that is usable by any layout parasitic capacitance (LPE) tool.