Simulation Standard

Silvaco面向半导体工艺和器件仿真工程师推出的技术刊物

Measurement of Spacing Checks in Guardian DRC

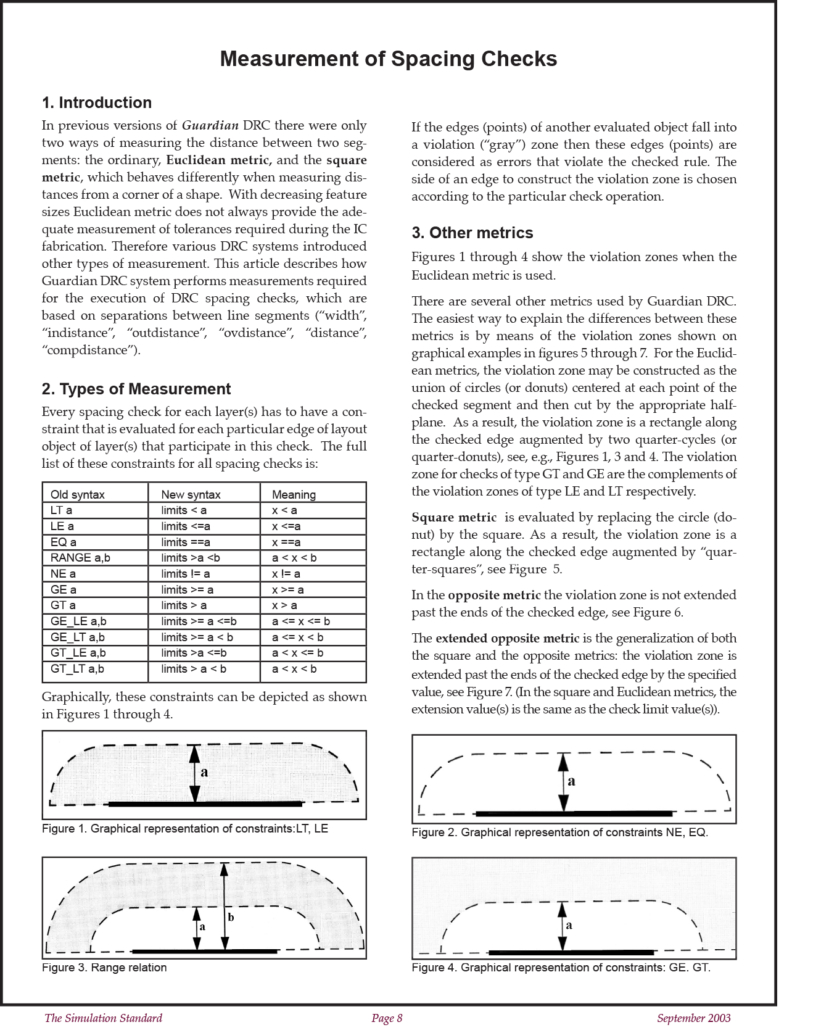

In previous versions of Guardian DRC there were only two ways of measuring the distance between two segments: the ordinary, Euclidean metric, and the square metric, which behaves differently when measuring distances from a corner of a shape. With decreasing feature sizes Euclidean metric does not always provide the adequate measurement of tolerances required during the IC fabrication. Therefore various DRC systems introduced other types of measurement. This article describes how Guardian DRC system performs measurements required for the execution of DRC spacing checks, which are based on separations between line segments (“width”, “indistance”, “outdistance”, “ovdistance”, “distance”, “compdistance”).

Highlighting Two Nodes in the Expert Layout Editor and Other Tips

Q: I would like to highlight two nodes at the same time in Expert. I currently use Verification->Node Probing->Pick Node to highlight a node, but I donít see how I can have 2 nets highlighted at the same time.

The Effect of Carrier Spilling on Spreading Resistance Profiling (SRP) Accuracy

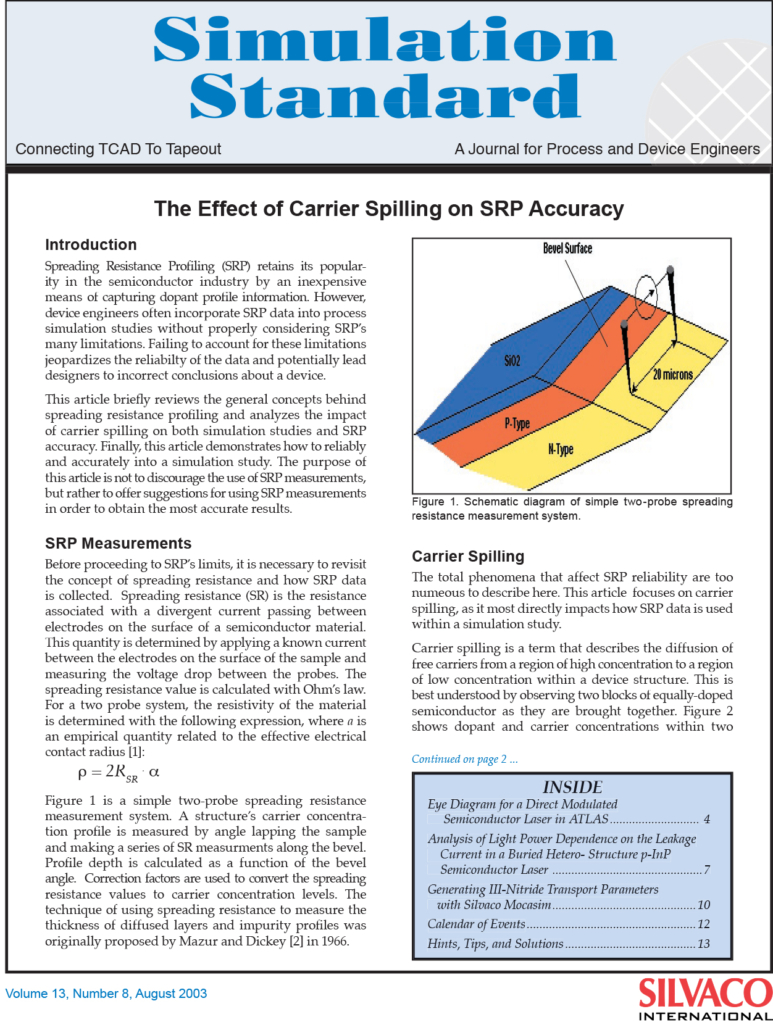

Spreading Resistance Profiling (SRP) retains its popularity in the semiconductor industry by an inexpensive means of capturing dopant profile information. However, device engineers often incorporate SRP data into process simulation studies without properly considering SRP’s many limitations. Failing to account for these limitations jeopardizes the reliability of the data and potentially lead designers to incorrect conclusions about a device.

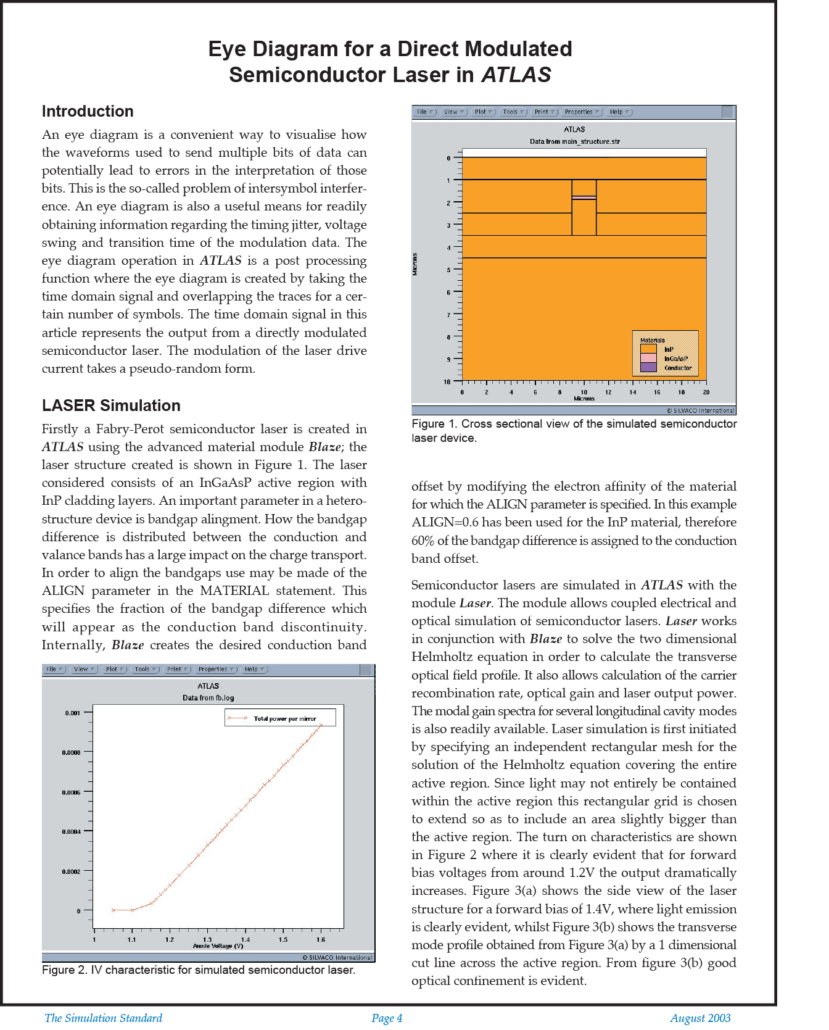

Eye Diagram for a Direct Modulated Semiconductor Laser in ATLAS

An eye diagram is a convenient way to visualise how the waveforms used to send multiple bits of data can potentially lead to errors in the interpretation of those bits. This is the so-called problem of intersymbol interference. An eye diagram is also a useful means for readily obtaining information regarding the timing jitter, voltage swing and transition time of the modulation data. The eye diagram operation in ATLAS is a post processing function where the eye diagram is created by taking the time domain signal and overlapping the traces for a certain number of symbols. The time domain signal in this article represents the output from a directly modulated semiconductor laser. The modulation of the laser drive current takes a pseudo-random form.

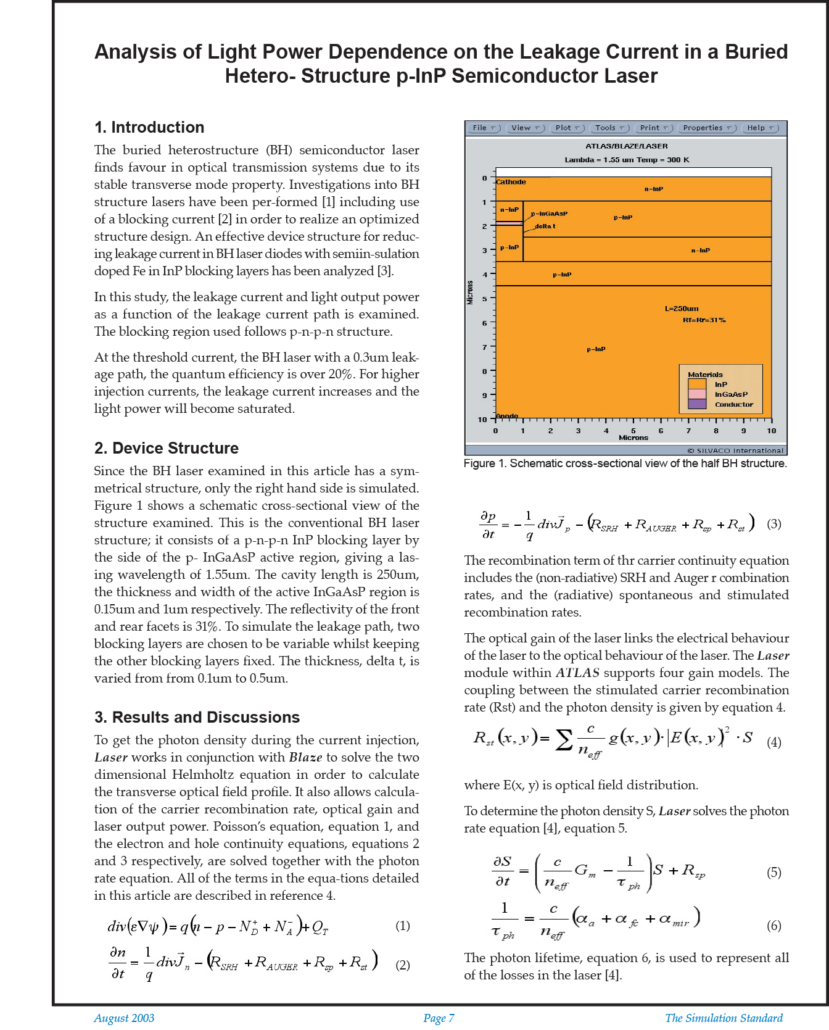

Analysis of Light Power Dependence on the Leakage Current in a Buried Hetero- Structure p-InP Semiconductor Laser

An effective device structure for reducing leakage current in BH laser diodes with semiin-sulation doped Fe in InP blocking layers has been analyzed [3]. In this study, the leakage current and light output power as a function of the leakage current path is examined. The blocking region used follows p-n-p-n structure.

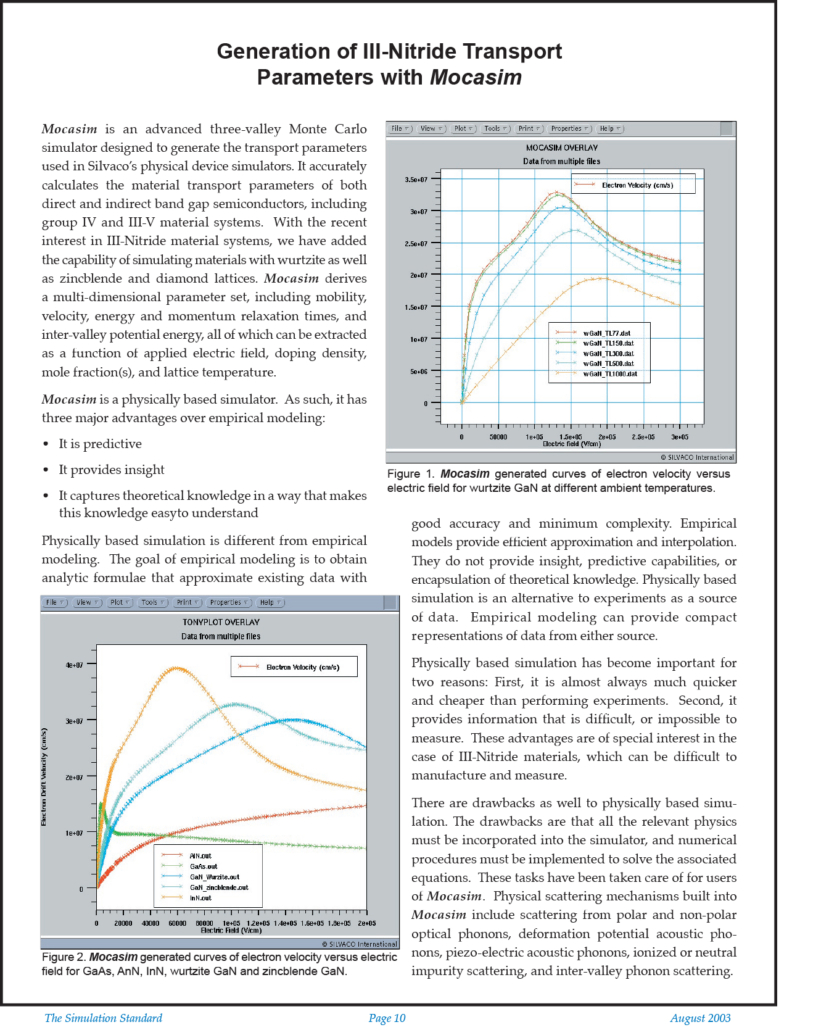

Generation of III-Nitride Transport Parameters with Mocasim

Mocasim is an advanced three-valley Monte Carlo simulator designed to generate the transport parameters used in Silvaco’s physical device simulators. It accurately calculates the material transport parameters of both direct and indirect band gap semiconductors, including group IV and III-V material systems. With the recent interest in III-Nitride material systems, we have added the capability of simulating materials with wurtzite as well as zincblende and diamond lattices. Mocasim derives a multi-dimensional parameter set, including mobility, velocity, energy and momentum relaxation times, and inter-valley potential energy, all of which can be extracted as a function of applied electric field, doping density, mole fraction(s), and lattice temperature.