Simulation Standard

Silvaco面向半导体工艺和器件仿真工程师推出的技术刊物

Using Victory Process to Create Realistic Structures for Capacitance Extraction in Clever

Silvaco offers many alternatives for creating simple 3D structures, the optimum choice depending on what the user needs to simulate. Many of the choices for creating simple 3D structures are for user convenience, so that just a single tool can both create the simple 3D structure and simulate the required physics. This gives the user an enhanced feeling of a tightly integrated product.

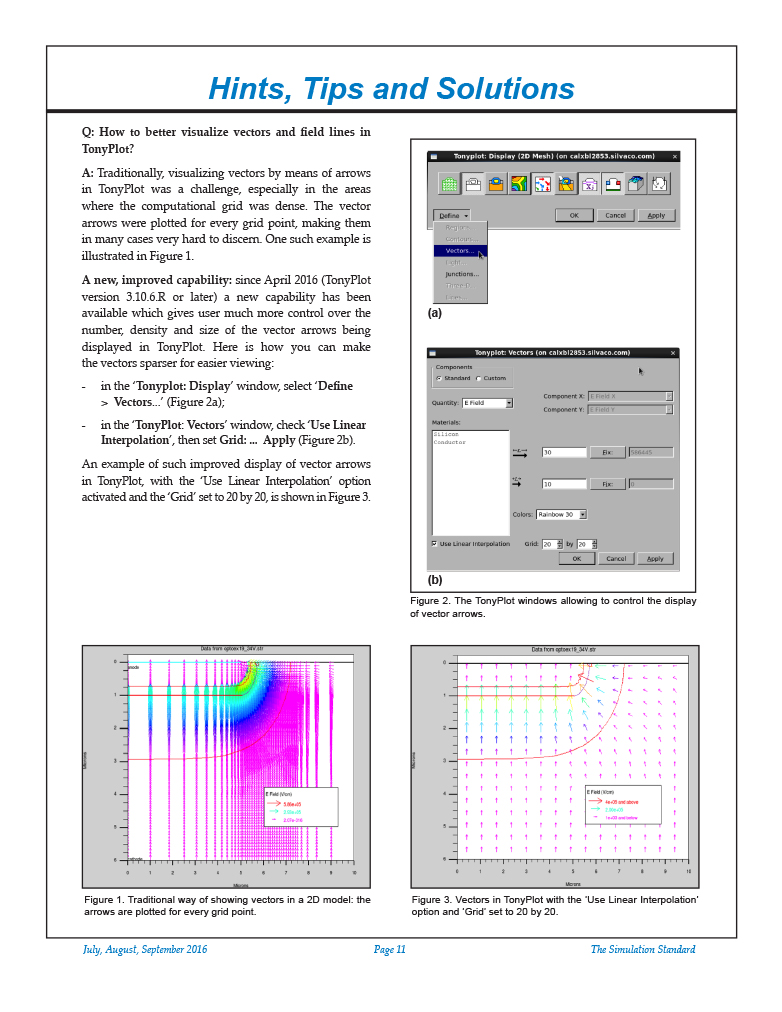

Hints, Tips and Solutions – How to best visualize vectors and field lines in TonyPlot

Traditionally, visualizing vectors by means of arrows in TonyPlot was a challenge, especially in the areas where the computational grid was dense. The vector arrows were plotted for every grid point, making them in many cases very hard to discern. One such example is illustrated in Figure 1.

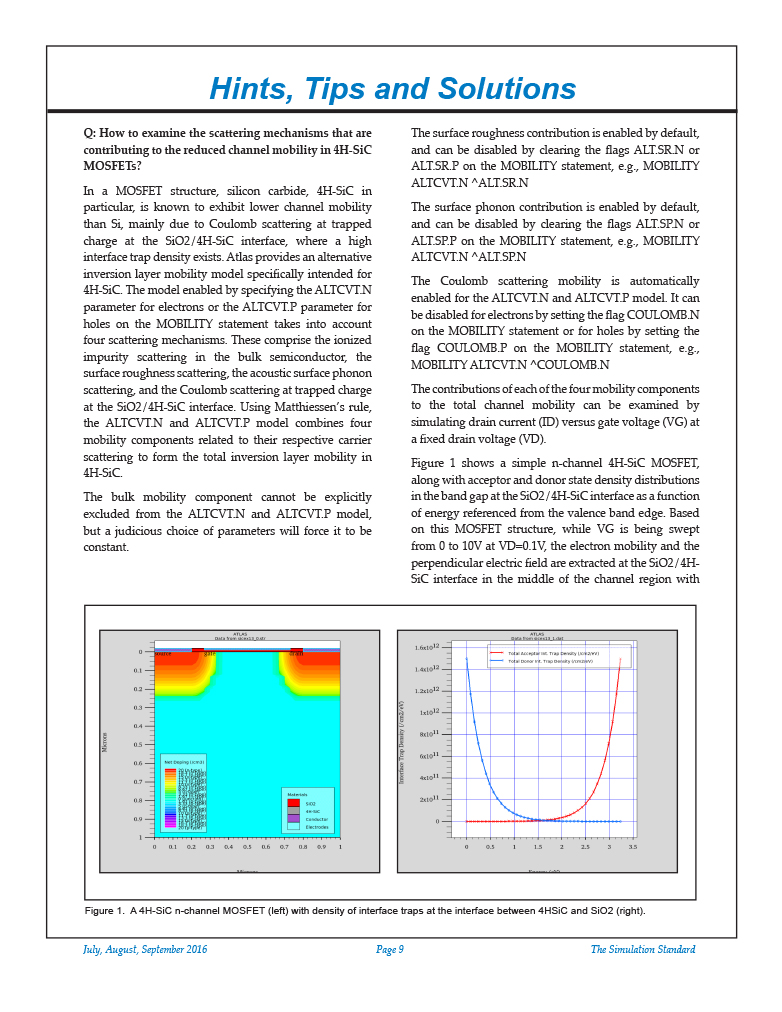

Hints, Tips and Solutions – Scattering mechanisms contributing to reduced channel mobility in 4H-SiC MOSFETs

In a MOSFET structure, silicon carbide, 4H-SiC in particular, is known to exhibit lower channel mobility than Si, mainly due to Coulomb scattering at trapped charge at the SiO2/4H-SiC interface, where a high interface trap density exists. Atlas provides an alternative inversion layer mobility model specifically intended for 4H-SiC. The model enabled by specifying the ALTCVT.N parameter for electrons or the ALTCVT.P parameter for holes on the MOBILITY statement takes into account four scattering mechanisms. These comprise the ionized impurity scattering in the bulk semiconductor, the surface roughness scattering, the acoustic surface phonon scattering, and the Coulomb scattering at trapped charge at the SiO2/4H-SiC interface. Using Matthiessen’s rule, the ALTCVT.N and ALTCVT.P model combines four mobility components related to their respective carrier scattering to form the total inversion layer mobility in 4H-SiC.

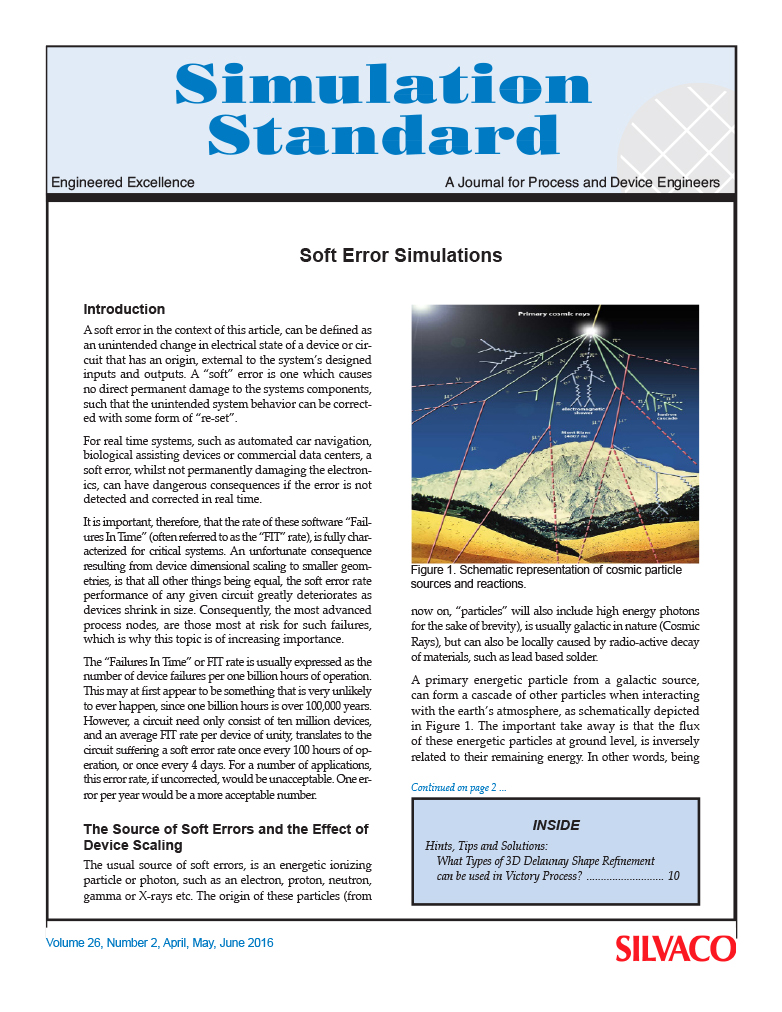

Soft Error

A soft error in the context of this article, can be defined as an unintended change in electrical state of a device or circuit, that has an origin, external to the system’s designed inputs and outputs. A “soft” error is one which causes no direct permanent damage to the systems components, such that the unintended system behavior can be corrected with some form of “re-set”.

Hints, Tips and Solutions – Types of 3D Delaunay Shape Refinement

Q: What Types of 3D Delaunay Shape Refinement can be used in Victory Process?

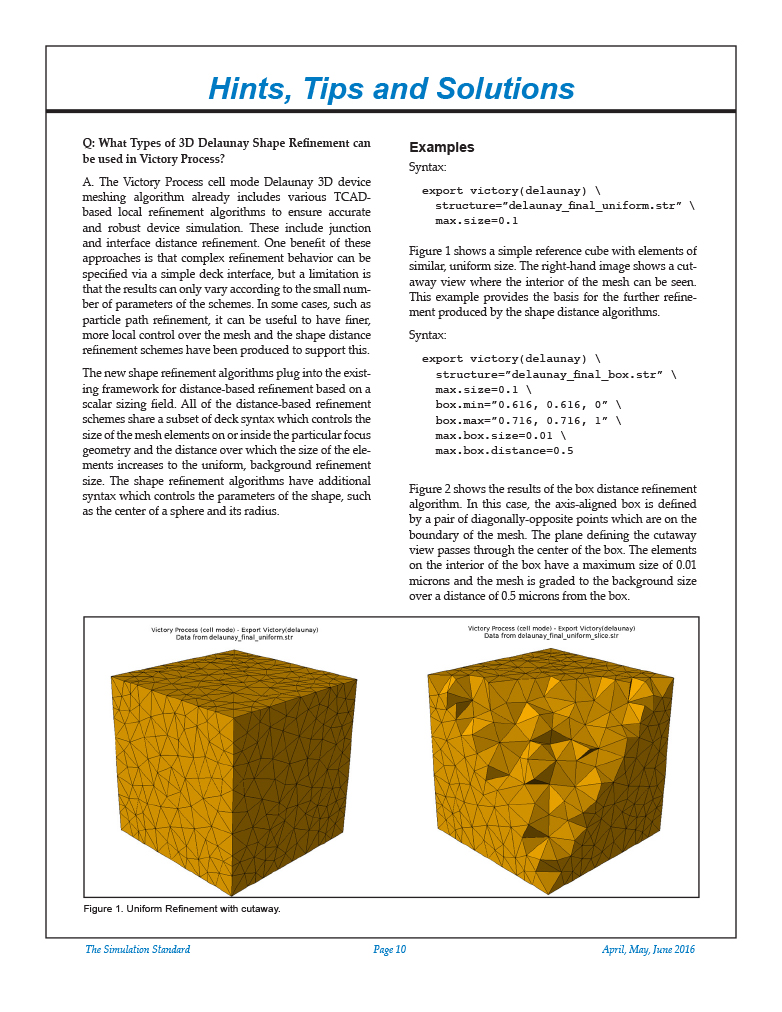

A. The Victory Process cell mode Delaunay 3D device meshing algorithm already includes various TCAD-based local refinement algorithms to ensure accurate and robust device simulation. These include junction and interface distance refinement. One benefit of these approaches is that complex refinement behavior can be specified via a simple deck interface, but a limitation is that the results can only vary according to the small number of parameters of the schemes. In some cases, such as particle path refinement, it can be useful to have finer, more local control over the mesh and the shape distance refinement schemes have been produced to support this.

Blue LED Simulation

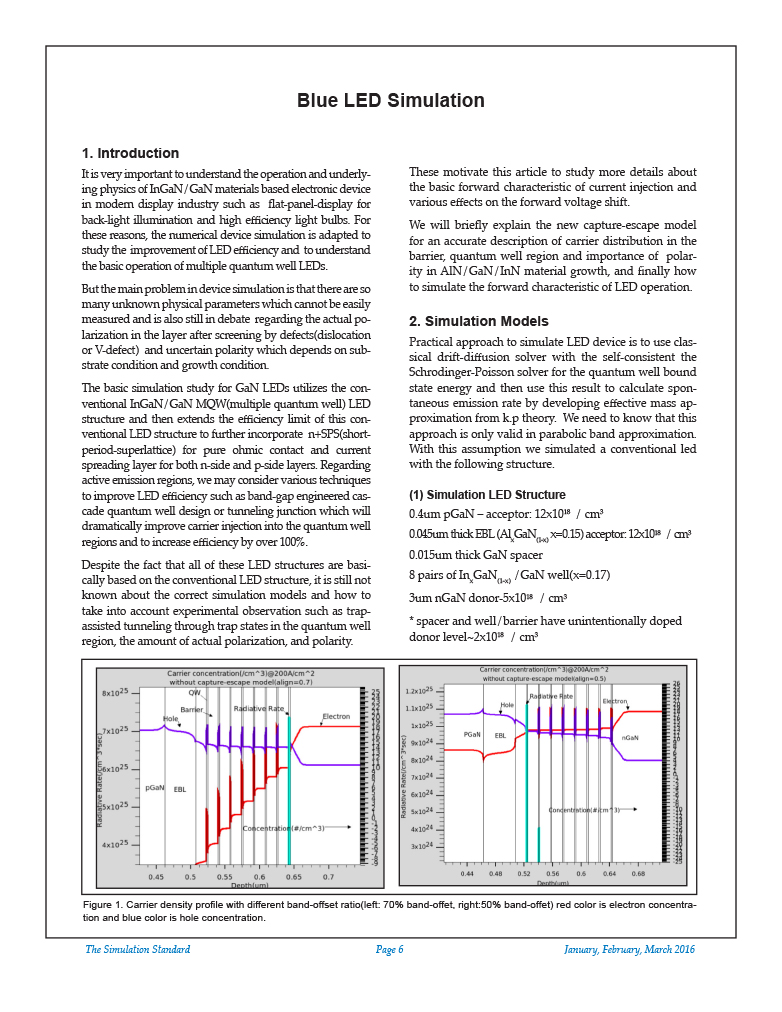

It is very important to understand the operation and underlying physics of InGaN/GaN materials based electronic device in modern display industry such as flat-panel-display for back-light illumination and high efficiency light bulbs. For these reasons, the numerical device simulation is adapted to study the improvement of LED efficiency and to understand the basic operation of multiple quantum well LEDs.