标准单元库特征化和偏差建模

概述

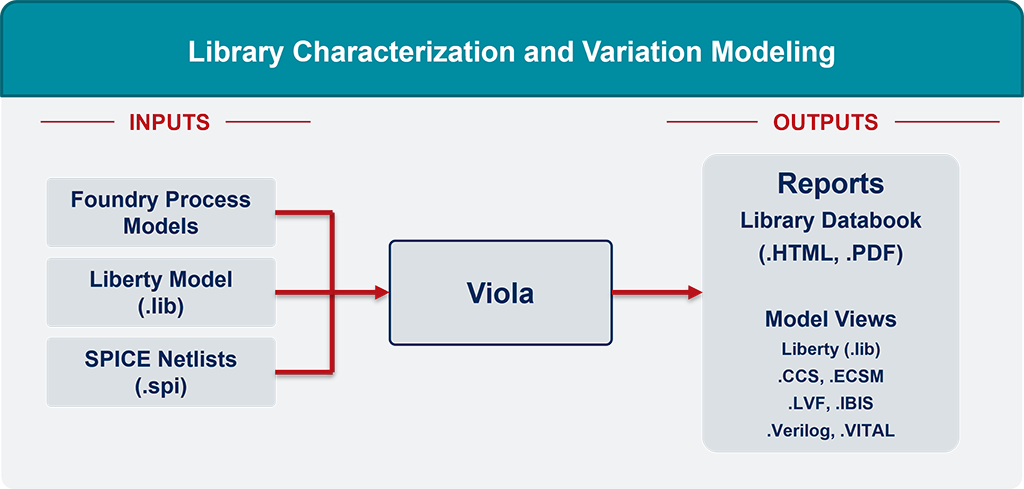

Viola 是一个独特的、整体的解决方案,可以对数字单元库、I/O 单元进行快速、准确地特征化建库。整体解决方案中含有Silvaco SmartSpice 仿真器,可以自动产生激励源、检查库模型和生成数据手册。

单元库特征化引擎会进行详细的单元电路分析,自动确定所需的激励,并使用SPICE来验证测量组合电路和时序电路的所有特性。

单元库质量管理系统保证了单元库文件质量合格,并根据一系列测试电路进行评估,确保SPICE级别的准确性和与静态时序分析的相关性。

单元库质量管理

Viola具有单元库质量管理功能,根据一系列测试电路对特征库进行鉴定和评估,以确保静态时序分析(STA)的结果和Sign-off获得的结果准确一致。Viola可以生成一份比较报告,明确指出哪些需要改进。

Viola 单元库特征化流程

主要功能特性与优点:

- 与SmartSpice模拟器和Silvaco工具紧密的集成

- 与HSPICE®和Spectre®模拟器完全集成

- 通过电流源建模(CCS和ECSM)对定时、功率和噪声进行高级表征,确保表征的准确性

- 在先进工艺节点使用LVF格式支持对工艺敏感的时序模型来提高性能优化

- 自动识别数字单元SPICE网表的数字单元

- 根据单元的参数和功能,Viola可以全自动生成涵盖所有逻辑组合的SPICE仿真文件

- 通过自定义激励和测量方法来完成对复杂的非标准单元的特性抽取

- 根据用户定义的约束条件自动确定查找表范围和索引

- 与Silvaco Liberty Analyzer中的Databook Generator完全集成,便于使用HTML浏览器来对提供分层数据库

- 强大的Tcl和Perl脚本环境

完整性

- 对于非线性延迟模型(NLDM)和电流源模型(CCS和ECSM),Viola可以提供二维和三维查的查找表

- 通过前级单元的驱动情况和PWL波形精确生成输入波形

- 通过LSF/SGE/OGE可并行进行SPICE仿真

- 对于常用设置提供直观的向导界面,并且为更多特征参数提供丰富的高级配置选项

- 激励、结果和模型的内置验证

- 验证Liberty约束值是否与输入设置相匹配

- 通过工艺角和模型进行一致性检查

- 重新定义任何现有Liberty文件的特征

- 生成的数据库可以提供HTML和PDF输出

- 完全支持Perl和Tcl脚本接口

单元类型

- 单端输出和多端输出组合单元,包括差分单元和三态输出单元

- 时序和组合成的one-hot单元

- 时序和组合多数位单元

- 复杂锁存器和触发器,包括SR锁存器和触发器

- 低功耗单元,如常开、电平移位器、电源开关和保持触发器

- 有多个电源供电的I/O pad

- 自定义单元

测量

- 不同状态的传播延迟和输出的传输延时

- 最小脉冲宽度

- 建立时间、保持时间、恢复时间和清除时间

- 根据内部静态、动态、开关、漏电和平均功率

- 输入引脚电容

- CCS和ECSM模型的时序、功率和噪声

- 零周期检查

输入

- Liberty™库模型文件

- 提取单元的网表

- 晶圆制造厂提供晶体管模型

输出

- 包括时序、电源和噪声信息的库文件

- 包括精度要求比较高的LVF模型单元库文件

- I/O的IBIS模型

- Verilog和VITAL

- HTML和PDF格式的数据手册

On-Chip Variation and the Sign-off Timing Flow: An Industry Perspective

Nanometer Library Characterization: Challenges and Solutions

Standard Cell Layout Migration and Optimization