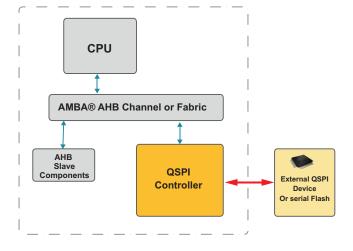

## AHB Quad SPI Controller with Execute in Place (XIP)

The Quad Serial Peripheral Interface module either controls a serial data link as a master component, or reacts to a serial data link as a slave component.

The IPC-QSPI-AHB bus controller can be configured under software control to be a master component or slave component device. Reading and writing the core is done on the AMBA AHB bus interface. The core operates in various data modes from 4 bits to 32 bits (8 modes are supported in multiples of 4 data bits). The data is then serialized and then transmitted, either LSB or MSB first, using the standard 4-wire SPI bus interface or the extended Quad mode bus.

## **Features**

- 4 bit to 32 bit serial transmit & receive

- Full and half duplex modes

- Software programmable Master component or Slave component mode

- · Software programmable SCLK rate for Master mode

- Quad-bit mode operation

- Dual-bit mode operation

- 64 word Tx and Rx FIFOs

- Asynchronous Slave component Interface

- AMBA AHB interface

- Interrupt control

- LSB or MSB mode

- Up to 4 slave components under Master component control

- DMA Interface

- · Compatible with many industry-standard FLASH devices

- Execute-in-place (XIP) functionality for industry-standard FLASH devices

## **Deliverables**

- Verilog Source

- Complete Test Environment

For more information, please contact us at ip@silvaco.com.

sales @silvaco.com br\_sales @silvaco.com eusales @silvaco.com JAPAN KOREA TAIWAN SINGAPORE CHINA jpsales@silvaco.com krsales@silvaco.com twsales@silvaco.com sgsales@silvaco.com cn sales@silvaco.com

HEADQUARTERS 4701 Patrick Henry Drive, Bldg #23 Santa Clara, CA 95054

in f

Rev 012021\_05 70115 CALIFORNIA BRAZIL EUROPE

WWW.SILVACO.COM

AHB Bus Functional Model