## SILACO

## **AHB** Arbiter

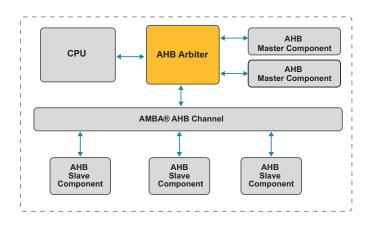

The AHB Arbiter arbitrates for the AHB bus among as many as four AHB master components. The AHB Arbiter implements a round-robin arbitration algorithm to AHB Master components that are requesting use of the bus. Only one master component may control a given phase of the AHB transaction at a given time.

AHB is a pipelined bus in which there are three distinct phases: Arbitration Phase, Address (or Control) Phase, and Data Phase. A consequence of pipelining is that these phases overlap in time. For example, it is possible that Master component A wins the Arbitration Phase that is coincident with the Address Phase owned by Master component B and the Data Phase owned by Master component C. It is in these terms that an AHB system must be discussed.

The AHB Arbiter has four distinct Mirrored-Master component Ports, each of which can be connected to an AHB Master components (e.g. a processor or a DMA Controller), and one Port that connects to an AHB subsystem, typically through an AHB Channel module.

## **Features**

- AMBA® 2.0 Compatible

- Supports up to 4 AHB Master components

- · Round Robin Arbitration

- Easily Expandable

## **Deliverables**

- Verilog Source

- Complete Test Environment

- · AHB Bus Functional Model

For more information, please contact us at ip@silvaco.com.

Rev 012021\_05