Pages

Full-Chip Parasitic Extraction

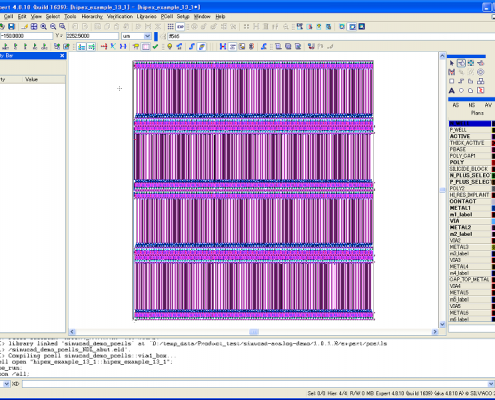

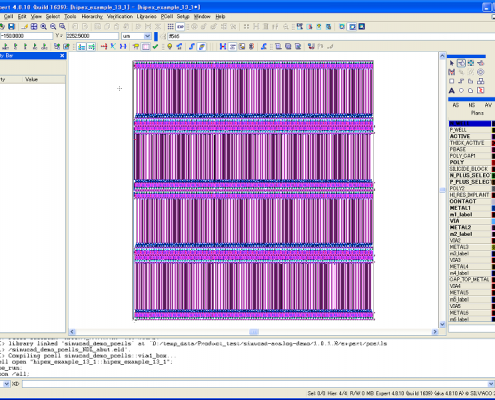

Hipex Full-chip Rule-based RC Parasitic Extraction

Hipex-RC provides an accurate and fast solution for the extraction of parasitic capacitance and resistance from hierarchical layouts of analog, mixed-signal, memory IC and SoC designs. As part of Silvaco’s complete analog custom design flow, RC parasitic extraction together with DRC/LVs is tightly integrated with the Silvaco Expert layout editor.

Parasitic Extraction

Clever

Clever is a TCAD-like script based solution, and is ideal for detailed extraction of cell layouts and is a physics-based resistance and capacitance field solver for any arbitrary 3D shaped structure