Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

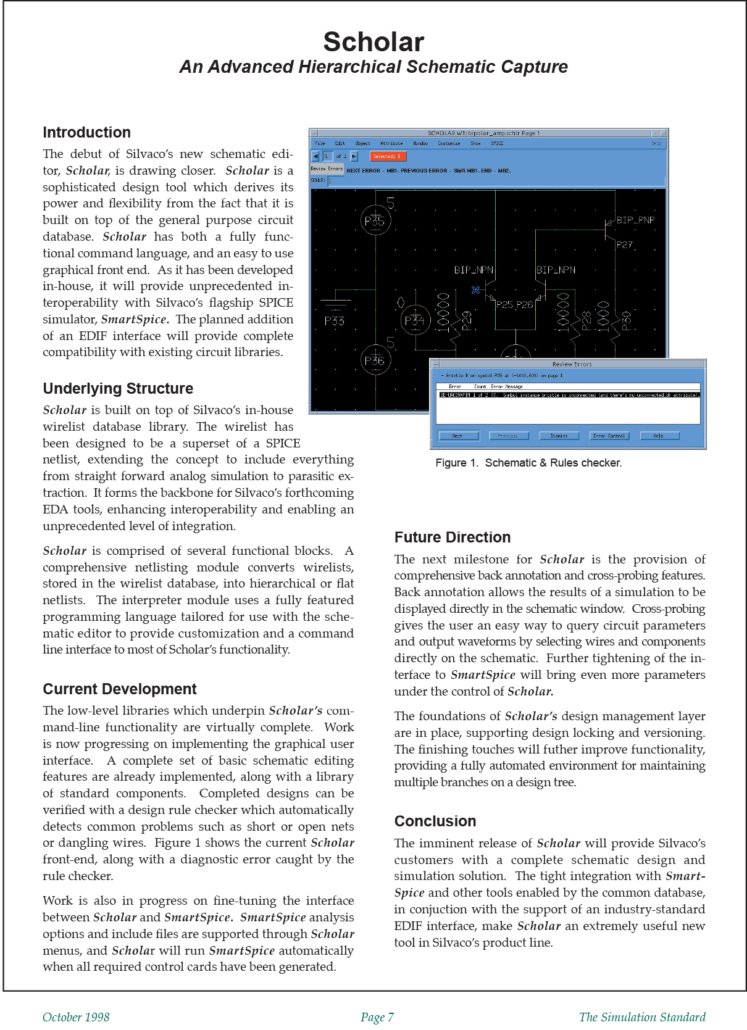

Scholar

The debut of Silvaco's new schematic editor, Scholar, is drawing closer. Scholar is a sophisticated design tool which derives its power and flexibility from the fact that it is built on top of the general purpose circuit database.

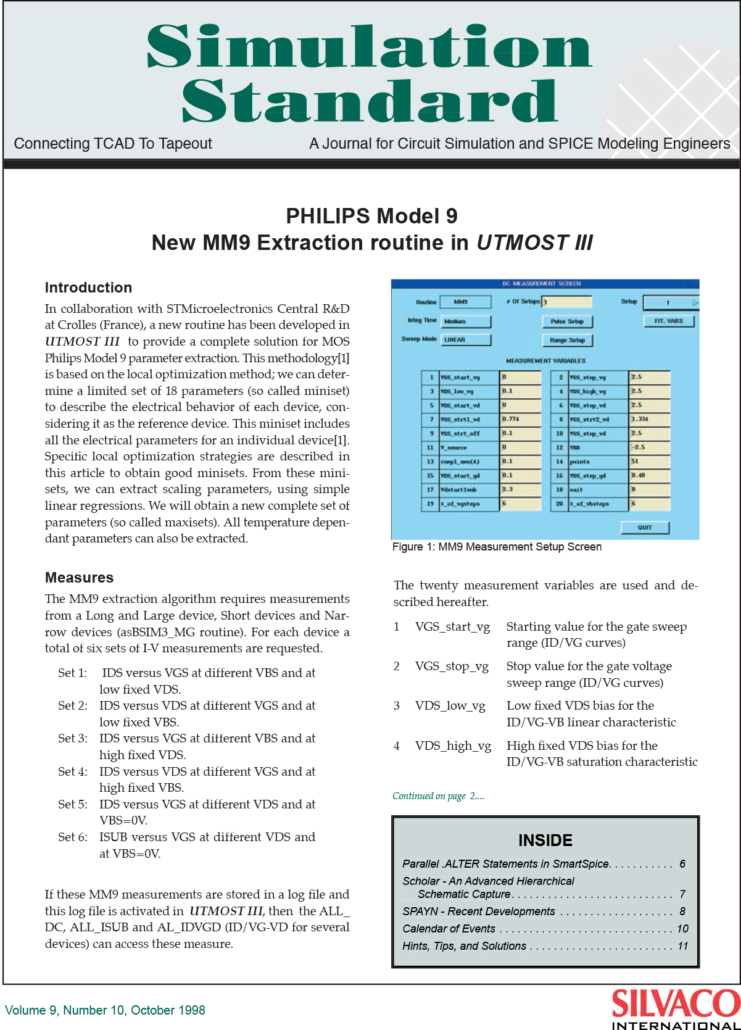

PHILIPS Model 9

In collaboration with STMicroelectronics Central R&D at Crolles (France), a new routine has been developed in UTMOST III to provide a complete solution for MOS Philips Model 9 parameter extraction. This methodology[1] is based on the local optimization method; we can determine a limited set of 18 parameters (so called miniset) to describe the electrical behavior of each device, considering it as the reference device.

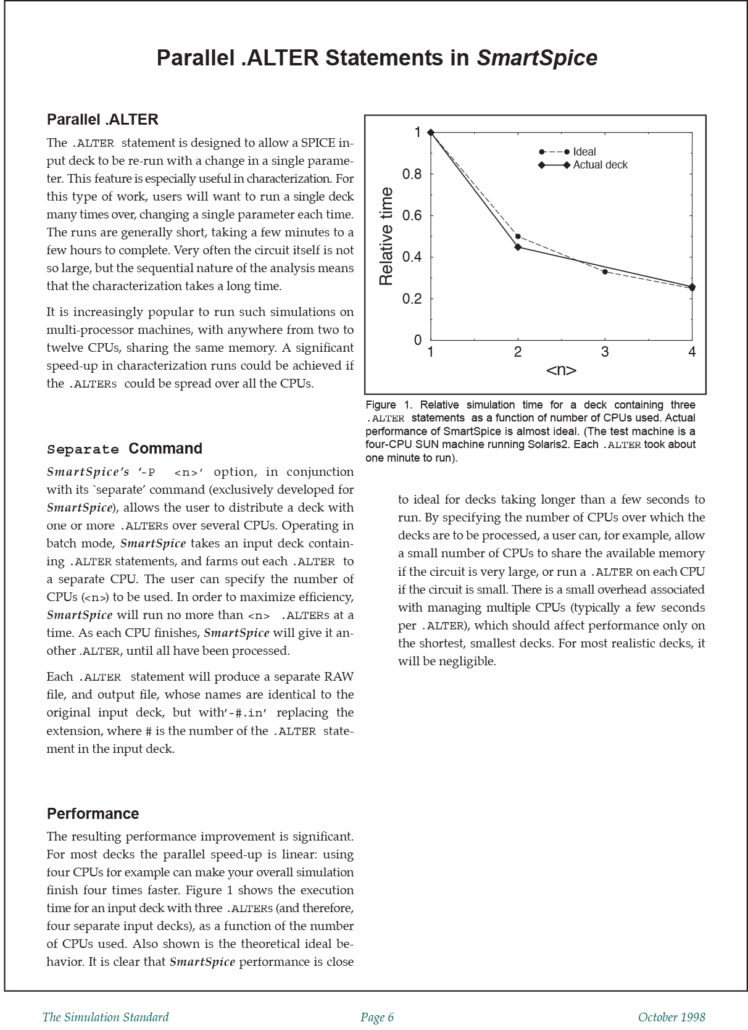

Parallel .ALTER Statements in SmartSpice

The .ALTER statement is designed to allow a SPICE input deck to be re-run with a change in a single parameter. This feature is especially useful in characterization. For this type of work, users will want to run a single deck many times over, changing a single parameter each time.

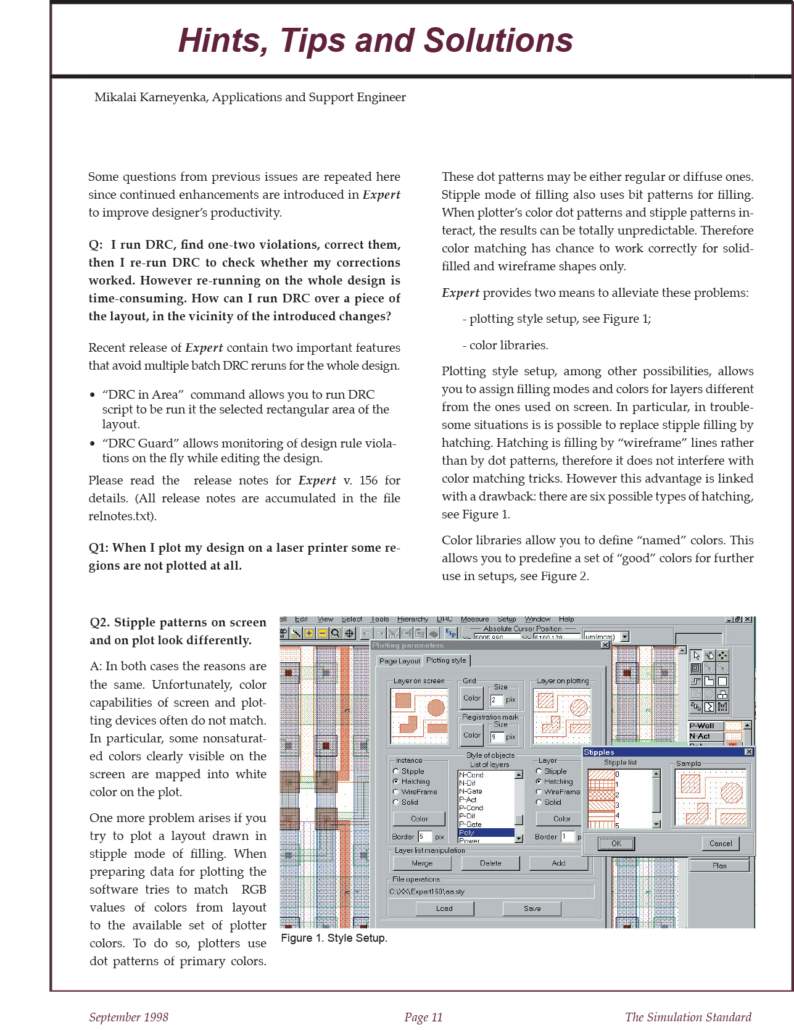

HINTS & TIPS – September 1998

I run DRC, find one-two violations, correct them, then I re-run DRC to check whether my corrections worked. However re-running on the whole design is time-consuming. How can I run DRC over a piece of the layout, in the vicinity of the introduced changes?

Recursive Cutting of Rectangular Partitions for VLSI Floorplanning

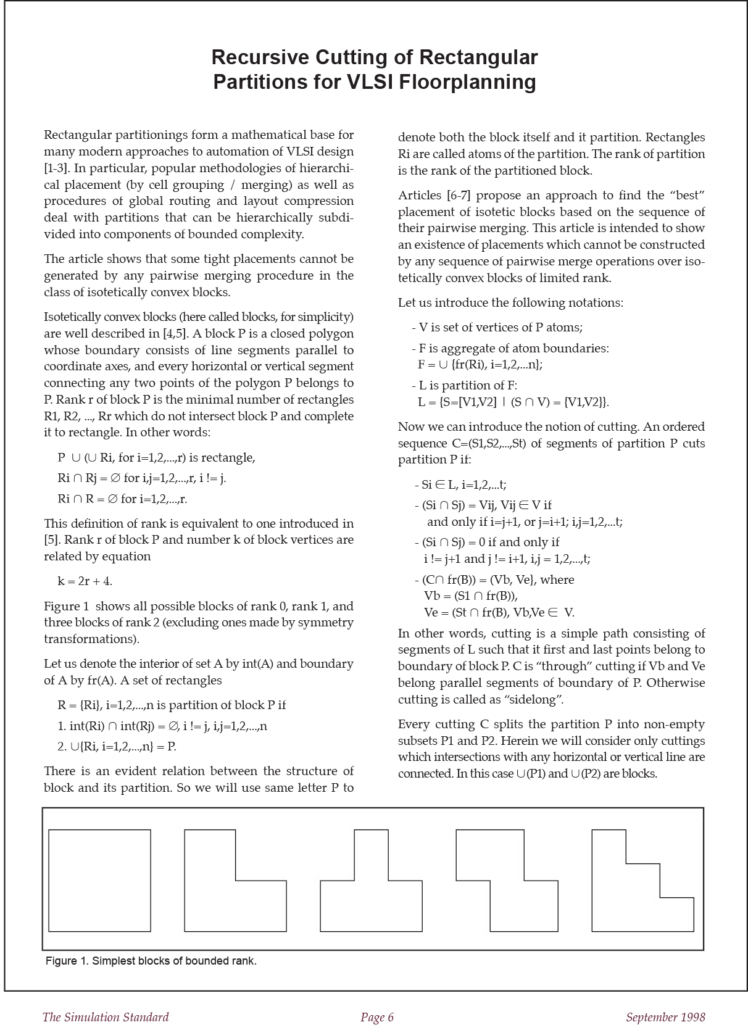

Rectangular partitionings form a mathematical base for many modern approaches to automation of VLSI design [1-3]. In particular, popular methodologies of hierarchical placement (by cell grouping / merging) as well as procedures of global routing and layout compression deal with partitions that can be hierarchically subdivided into components of bounded complexity.

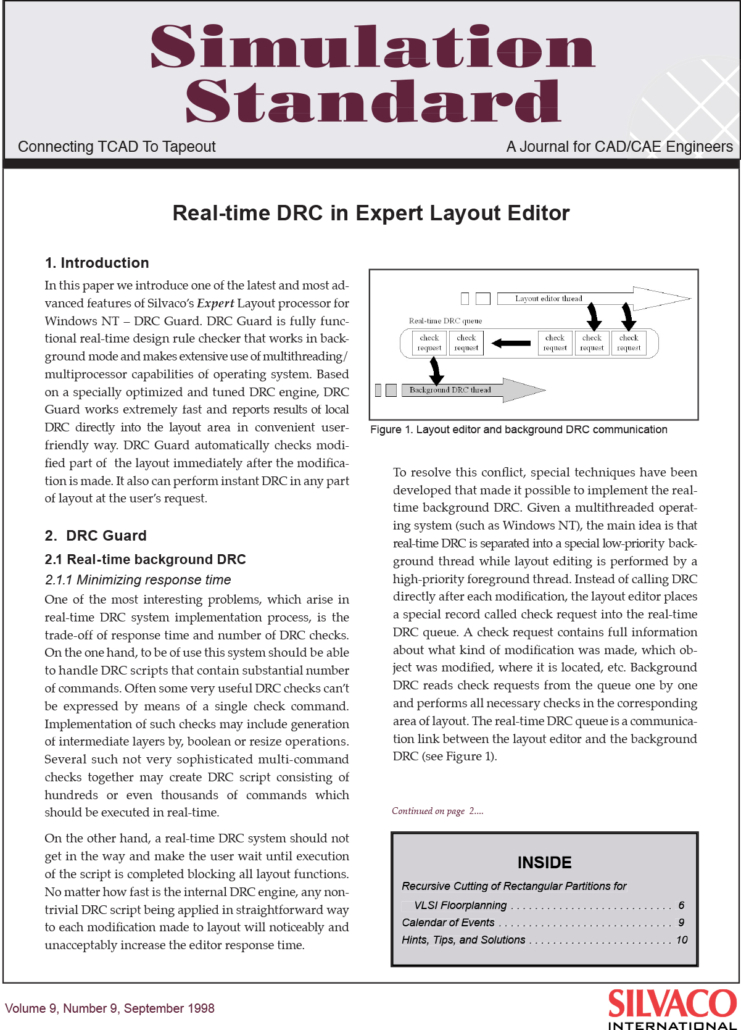

Real-time DRC in Expert Layout Editor

In this paper we introduce one of the latest and most advanced features of Silvaco's Expert Layout processor for Windows NT DRC Guard. DRC Guard is fully functional real-time design rule checker that works in background mode and makes extensive use of multithreading/ multiprocessor capabilities of operating system.