Simulation Standard Technical Journal

A Journal for Process and Device Engineers

Electrostatic Effect of Localized Charge in Dual Bit Memory Cells with DiscreteTraps

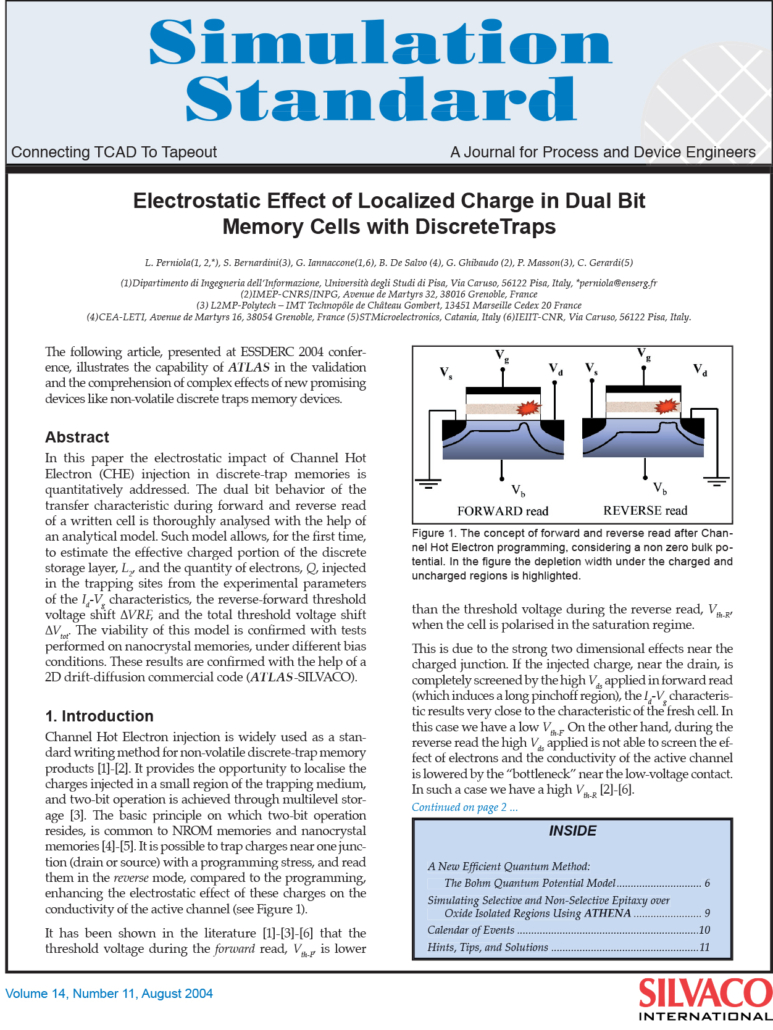

In this paper the electrostatic impact of Channel Hot Electron (CHE) injection in discrete-trap memories is quantitatively addressed. The dual bit behavior of the transfer characteristic during forward and reverse read of a written cell is thoroughly analysed with the help of an analytical model. Such model allows, for the first time, to estimate the effective charged portion of the discrete storage layer, L2, and the quantity of electrons, Q, injected in the trapping

A New Efficient Quantum Method: The Bohm Quantum Potential Model

This article presents a new approach to model the quantum confinement of carriers in MOSFET or heterostructure. SILVACO has already included in its device simulator ATLAS, a Schrödinger-Poisson solver and Density-Gradient model

The subject of how to use the EXTRACT statement in DeckBuild often arises

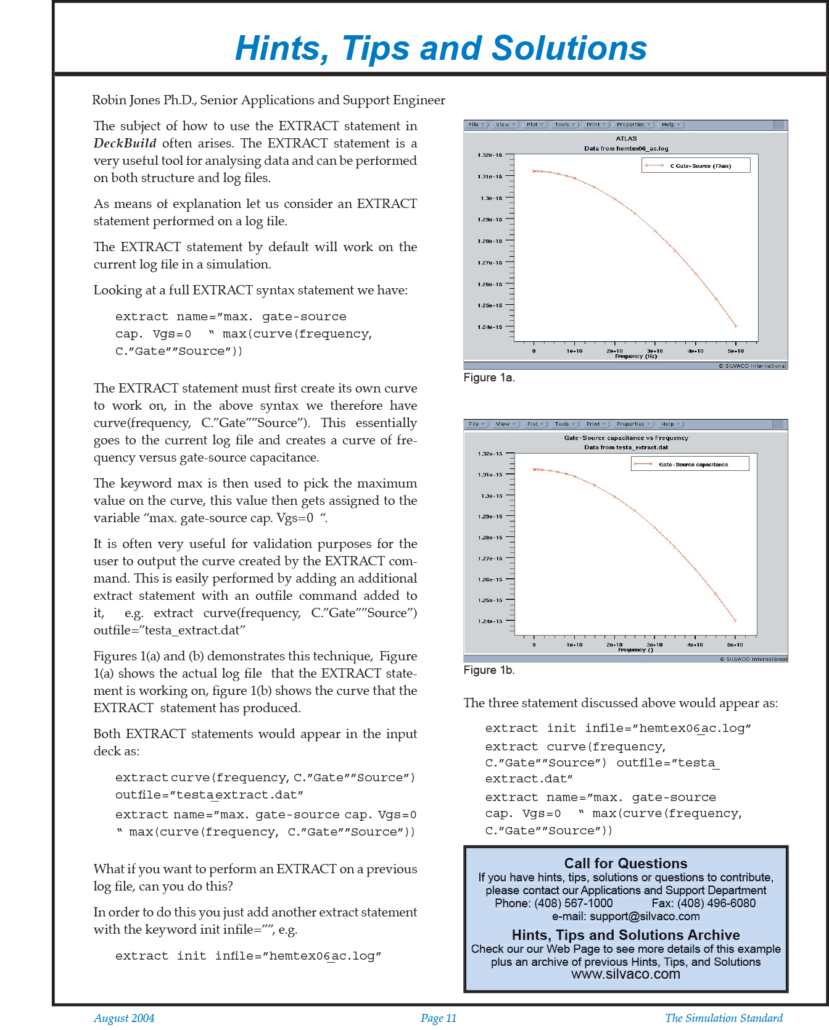

The subject of how to use the EXTRACT statement in DeckBuild often arises. The EXTRACT statement is a very useful tool for analysing data and can be performed on both structure and log files.

Simulating Selective and Non-Selective Epitaxy over Oxide Isolated Regions Using Athena

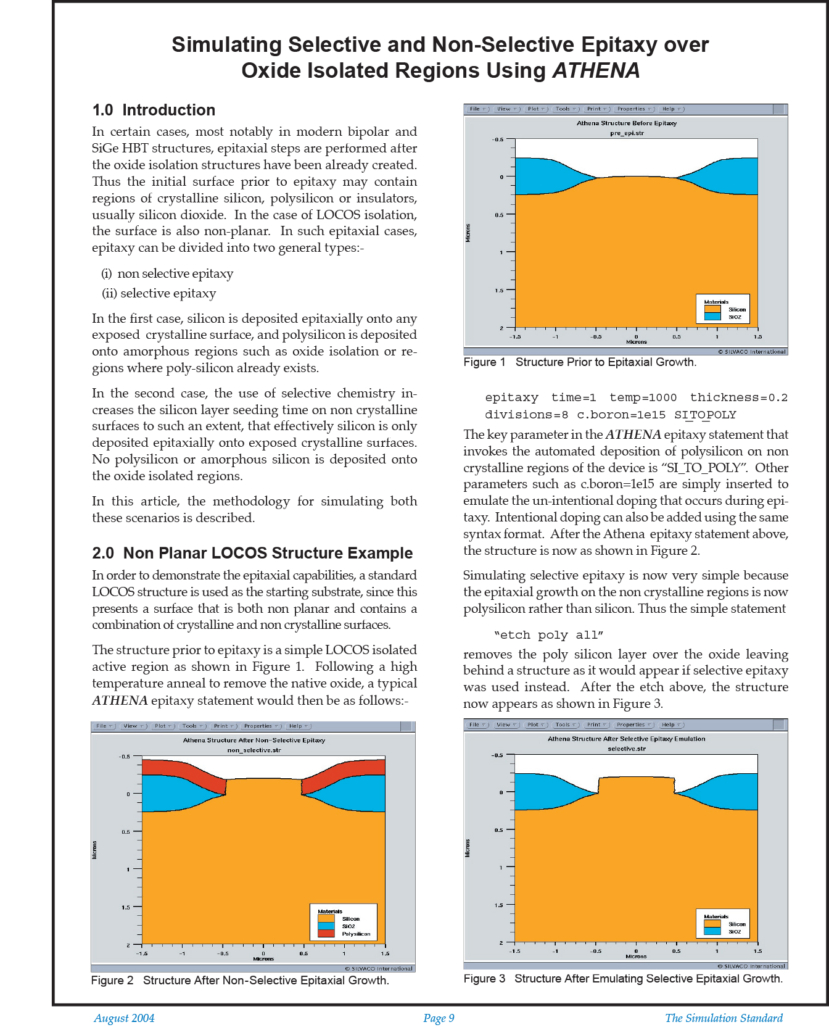

In certain cases, most notably in modern bipolar and SiGe HBT structures, epitaxial steps are performed after the oxide isolation structures have been already created. Thus the initial surface prior to epitaxy may contain regions of crystalline silicon, polysilicon or insulators, usually silicon dioxide. In the case of LOCOS isolation, the surface is also non-planar. In such epitaxial cases, epitaxy can be divided into two general types:-

Silvaco’s RFIC Design Suite

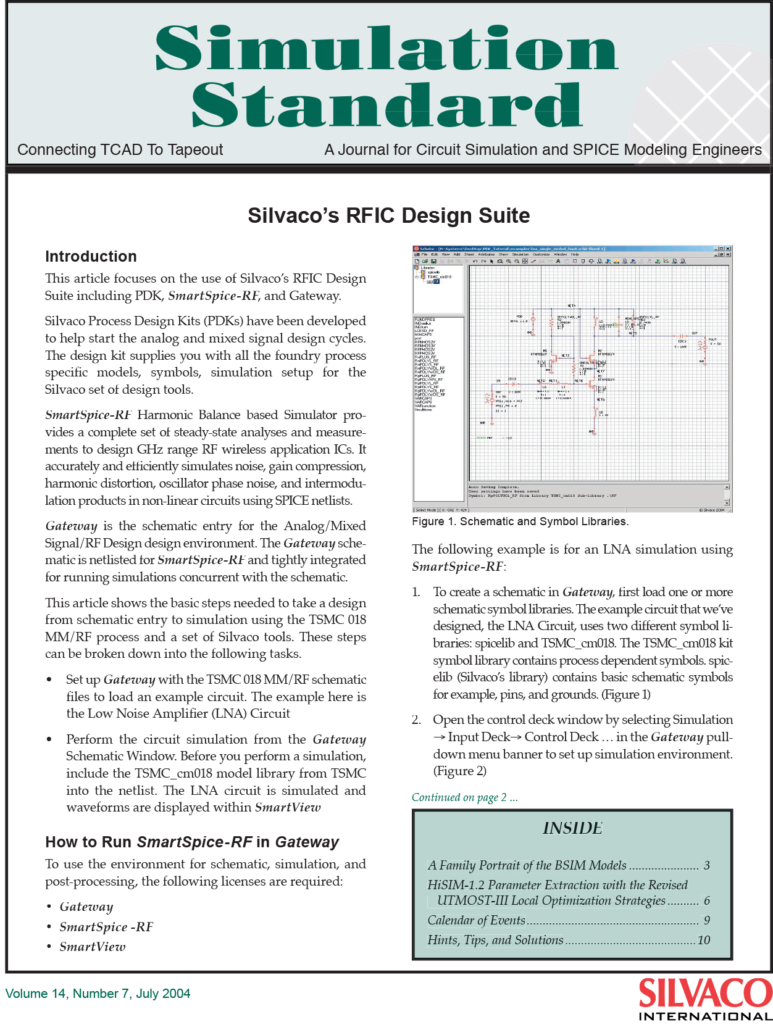

This article focuses on the use of Silvaco’s RFIC Design Suite including PDK, SmartSpice-RF, and Gateway.

HiSIM-1.2 Parameter Extraction with the Revised UTMOST-III Local Optimization Strategies

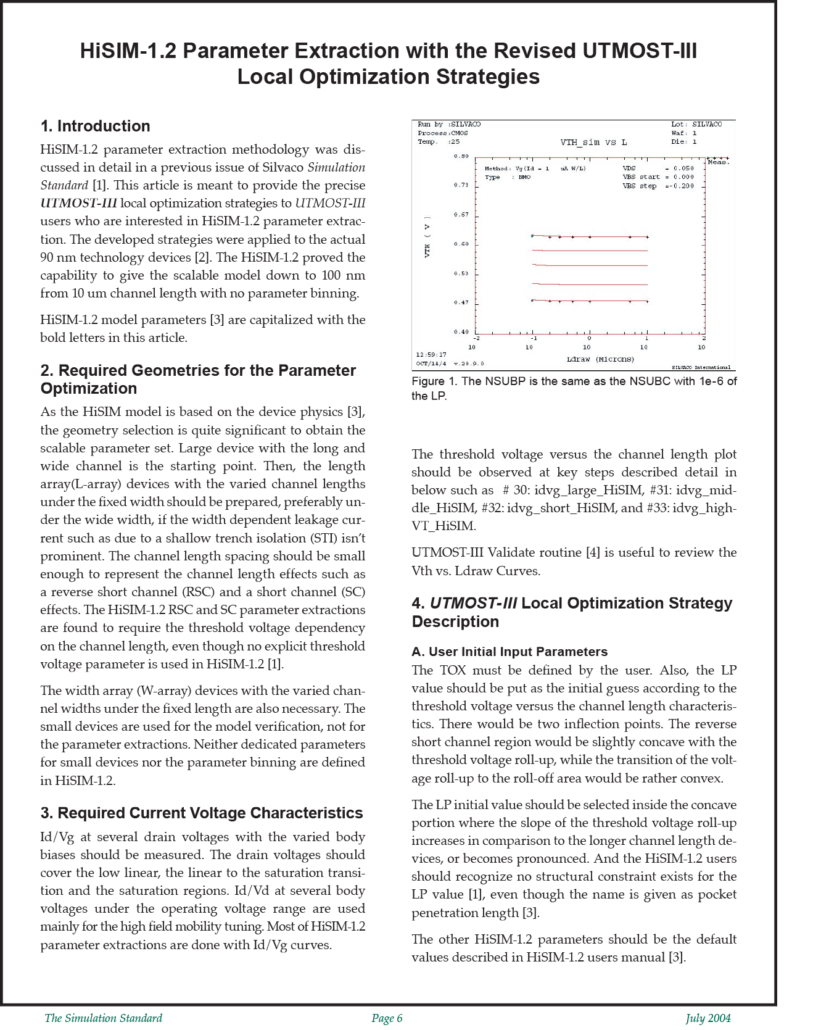

HiSIM-1.2 parameter extraction methodology was discussed in detail in a previous issue of Silvaco Simulation Standard [1]. This article is meant to provide the precise UTMOST-III local optimization strategies to UTMOST-III users who are interested in HiSIM-1.2 parameter extraction. The developed strategies were applied to the actual 90 nm technology devices [2]. The HiSIM-1.2 proved the capability to give the scalable model down to 100 nm from 10 um channel length with no parameter binning.