Simulation Standard Technical Journal

A Journal for Process and Device Engineers

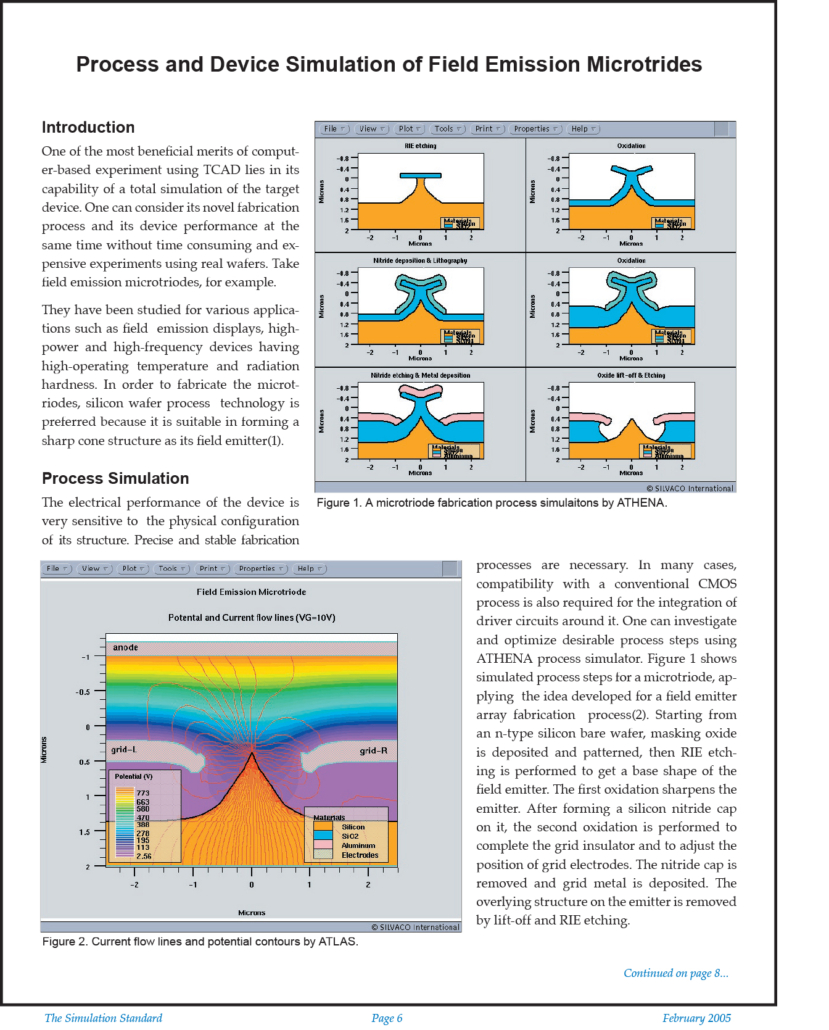

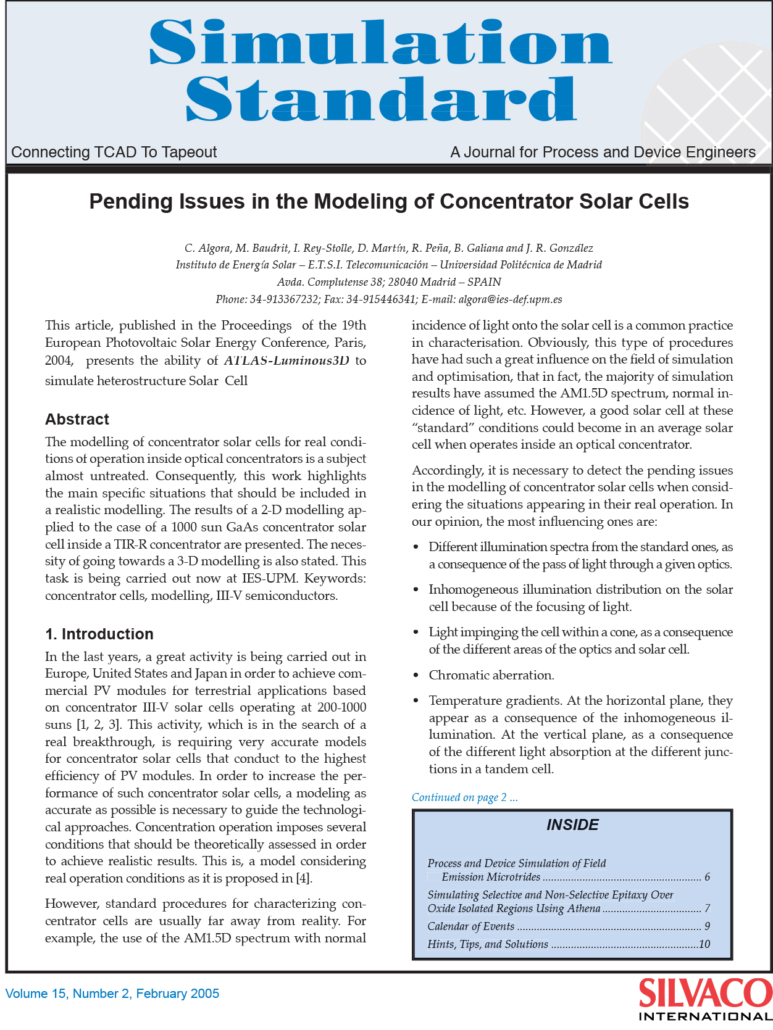

Process and Device Simulation of Field Emission Microtrides

One of the most beneficial merits of computer-based experiment using TCAD lies in its capability of a total simulation of the target device. One can consider its novel fabrication process and its device performance at the same time without time consuming and expensive experiments using real wafers. Take field emission microtriodes, for example.

Pending Issues in the Modeling of Concentrator Solar Cells

The modelling of concentrator solar cells for real conditions of operation inside optical concentrators is a subject almost untreated. Consequently, this work highlights the main specific situations that should be included in a realistic modelling. The results of a 2-D modelling applied to the case of a 1000 sun GaAs concentrator solar cell inside a TIR-R concentrator are presented. The necessity of going towards a 3-D modelling is also stated. This task is being carried out now at IES-UPM. Keywords: concentrator cells, modelling, III-V semiconductors.

How can I view a Foundry DRC run in Expert?

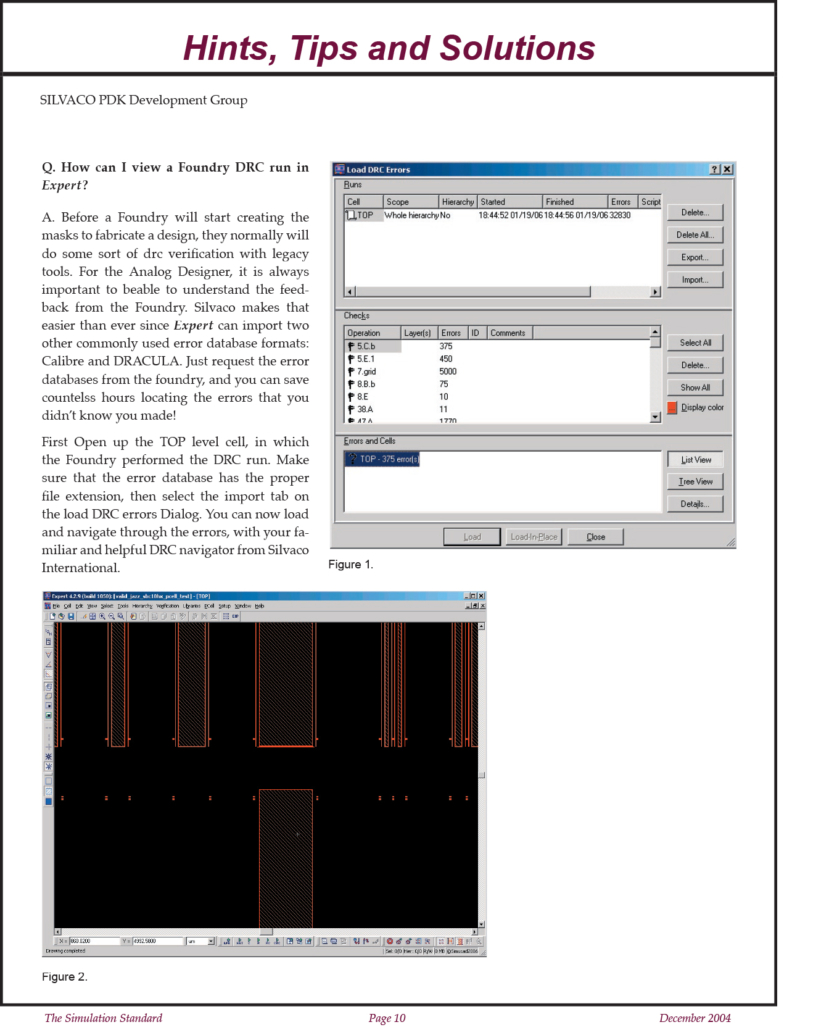

Q: How can I view a Foundry DRC run in Expert?

A: Before a Foundry will start creating the masks to fabricate a design, they normally will do some sort of drc verification with legacy tools. For the Analog Designer, it is always important to beable to understand the feedback from the Foundry. Silvaco makes that easier than ever since Expert can import two other commonly used error database formats: Calibre and DRACULA. Just request the error databases from the foundry, and you can save countelss hours locating the errors that you didn’t know you made!

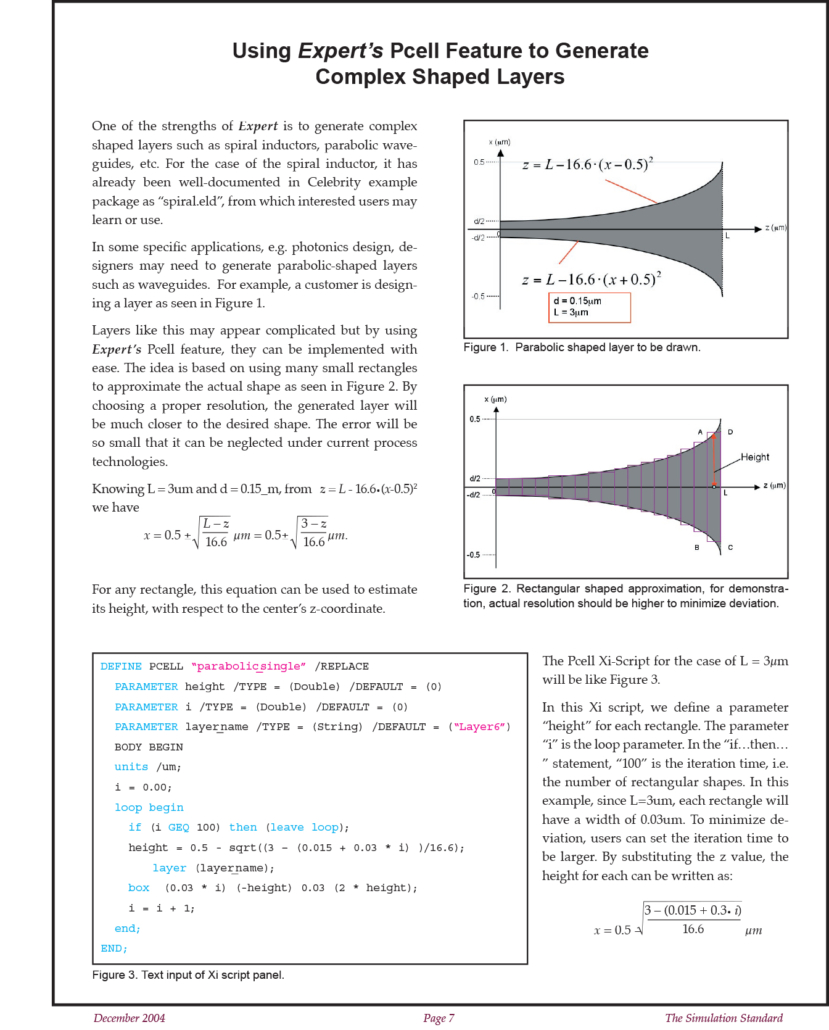

Using Expert’s Pcell Feature to Generate Complex Shaped Layers

One of the strengths of Expert is to generate complex shaped layers such as spiral inductors, parabolic waveguides, etc. For the case of the spiral inductor, it has already been well-documented in CELEBRITY example package as “spiral.eld”, from which interested users may learn or use.

Cross-Sectional Viewer

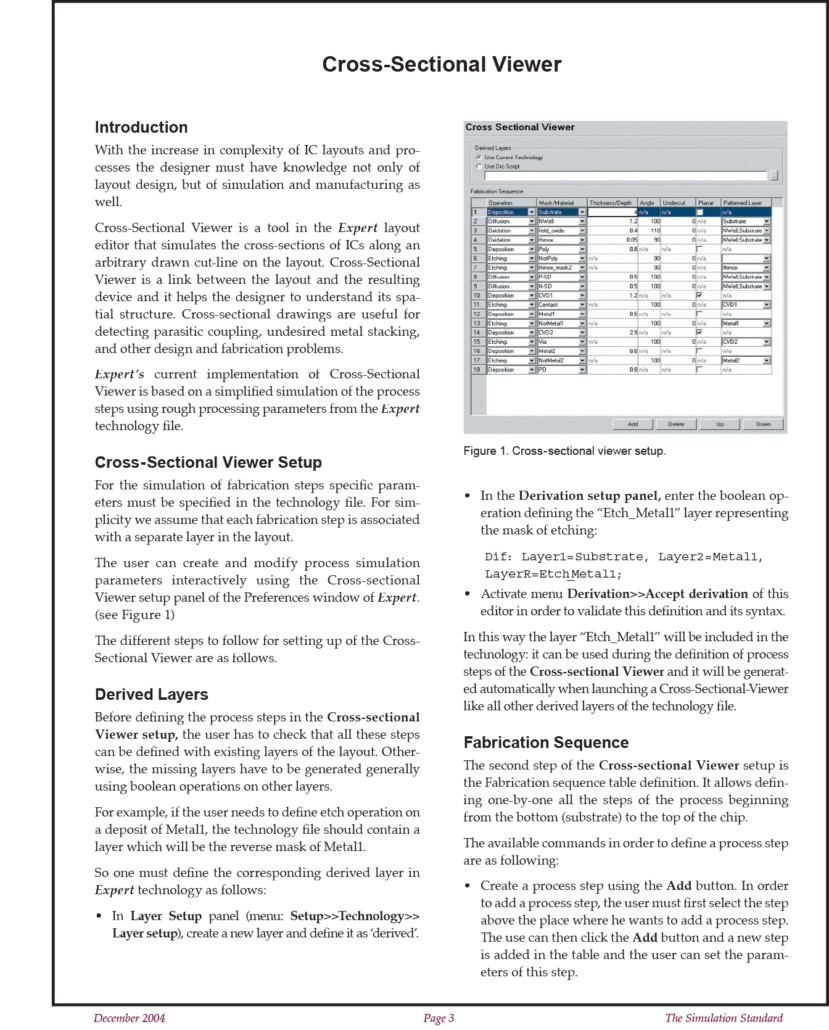

Cross-Sectional Viewer is a tool in the Expert layout editor that simulates the cross-sections of ICs along an arbitrary drawn cut-line on the layout. Cross-Sectional Viewer is a link between the layout and the resulting device and it helps the designer to understand its spatial structure. Cross-sectional drawings are useful for detecting parasitic coupling, undesired metal stacking, and other design and fabrication problems.

How do you perform a lift off procedure in ATHENA?

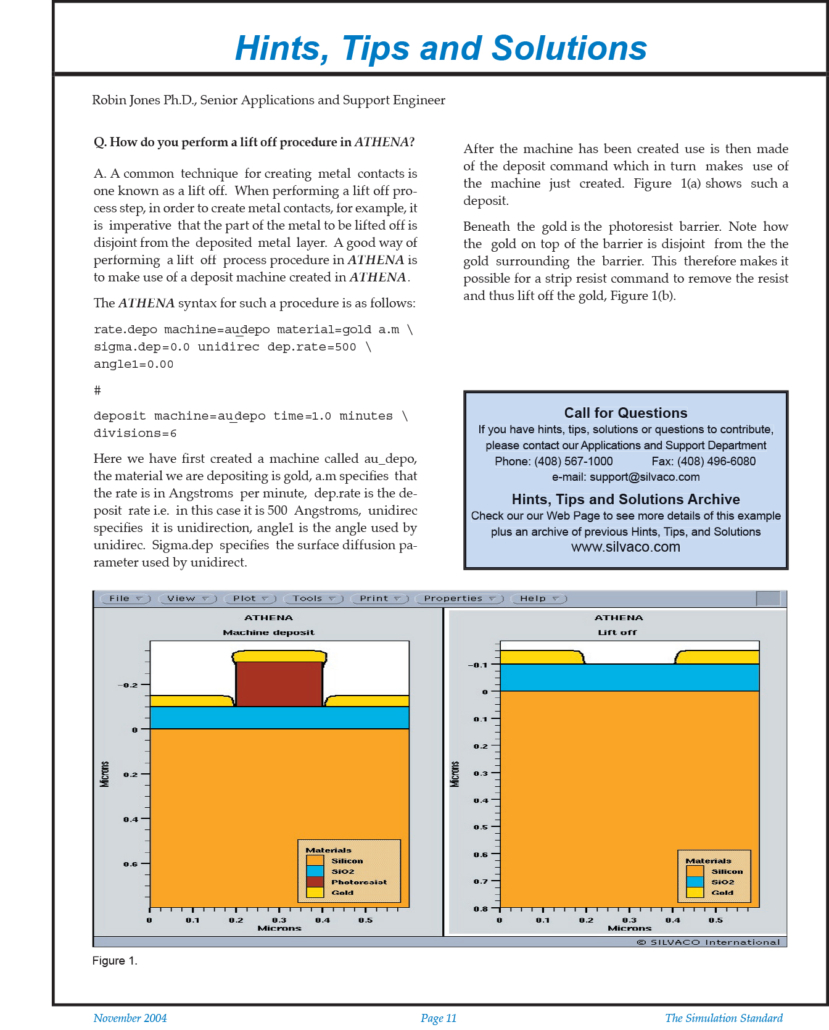

A common technique for creating metal contacts is one known as a lift off. When performing a lift off process step, in order to create metal contacts, for example, it is imperative that the part of the metal to be lifted off is disjoint from the deposited metal layer. A good way of performing a lift off process procedure in ATHENA is to make use of a deposit machine created in ATHENA.