Next Generation CMOS Nanowire: From Atoms to Circuit Simulation

Udita Kapoor, Sean C. Kelly, Mark Townsend, Derek Kimpton, and Eric Guichard1

Sebastien Martini, Thierry Poiroux, and Oliver Rozeau2

James Charles, Daniel Lemus, and Tillmann Kubis3

Silvaco, Inc. USA1, CEA-Leti France2, Purdue University – Indiana USA3

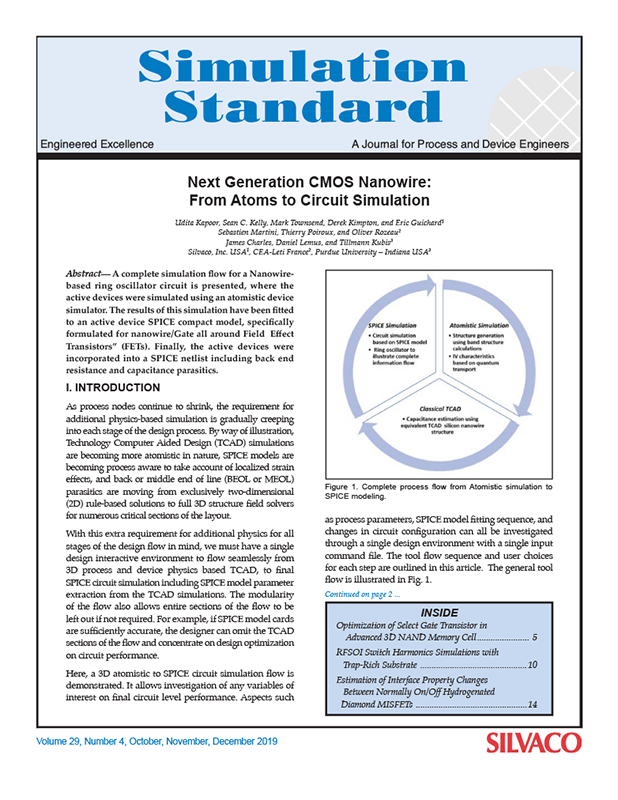

Abstract— A complete simulation flow for a Nanowire-based ring oscillator circuit is presented, where the active devices were simulated using an atomistic device simulator. The results of this simulation have been fitted to an active device SPICE compact model, specifically formulated for nanowire/Gate all around Field Effect Transistors” (FETs). Finally, the active devices were incorporated into a SPICE netlist including back end resistance and capacitance parasitics.

I. INTRODUCTION

As process nodes continue to shrink, the requirement for additional physics-based simulation is gradually creeping into each stage of the design process. By way of illustration, Technology Computer Aided Design (TCAD) simulations are becoming more atomistic in nature, SPICE models are becoming process aware to take account of localized strain effects, and back or middle end of line (BEOL or MEOL) parasitics are moving from exclusively two-dimensional (2D) rule-based solutions to full 3D structure field solvers for numerous critical sections of the layout.

With this extra requirement for additional physics for all stages of the design flow in mind, we must have a single design interactive environment to flow seamlessly from 3D process and device physics based TCAD, to final SPICE circuit simulation including SPICE model parameter extraction from the TCAD simulations. The modularity of the flow also allows entire sections of the flow to be left out if not required. For example, if SPICE model cards are sufficiently accurate, the designer can omit the TCAD sections of the flow and concentrate on design optimization on circuit performance.