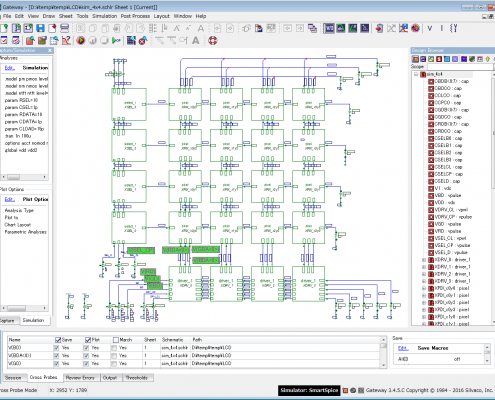

Gateway Schematic Editor

Gateway is Silvaco’s hierarchical schematic editor that provides an easy to use and feature-rich environment to visualize and capture analog, digital, mixed-signal and RF designs.

Introduction

Gateway is a highly productive environment with intuitive editing, capacity to support large and complex hierarchical or flat designs, ability to automatically generate symbols from existing legacy netlists and support for industry standard netlist and interface formats.

Gateway creates multiple views for design capture, simulation, layout and verification with interfaces to popular tools. These include SmartSpice, Silos, SmartView waveform viewer, Atlas, Victory Device, Expert and SmartDRC/LVS.

Powerful scripting capabilities enable users to customize the interface and create dedicated functions to meet individual and design team requirements.

Features

- Hierarchical multi-view, multi-sheet editor supports large and highly complex designs

- Edit-in place functions with wires, busses, bus ripping and bus merging

- Wire to wire, wire to pin, wire by name and implicit/global connections

- Cross-probing between waveform display and schematic

- View Info via hierarchy: Ability to trace signals via levels

- Configurable rule checks show electrical drawing rule and netlist violations

- Device parameter, DC bias and threshold displays

- Encryption support for intellectual property protection

Benefits

- Fast design creation and editing using intuitive and easy to use environment

- Flexibility to support many design flows and uses from same schematic source, with import/export supporting multiple netlist formats

- Easily conceptualize large hierarchical or flat designs with advanced naming capabilities for buses, instances and node names

Applications

- Analog and Digital blocks, mixed-signal, RF, Standard cells and IO’s

Technical Specifications

- Netlist format supported

- SPICE

- CDL

- NDL

- Verilog IEEE 1364

- Simulation environment supported

- SmartSpice

- HSPICE®

- Silos

- Device Simulators like Atlas and Victory Device

- OpenAccess and iPDK Support

- Interface with 3rd party schematic tools via EDIF 2 0 0

- Advanced scripting support using JavaScript, extended to provide access to 200 functions and allows to customize menu and GUI and to user callback symbol

- Extensive set of custom PDKs plus support for iPDK – contact Silvaco for latest information

Power Devices SPICE Modeling for Si, GaN and SiC Technologies

Learn About Advanced TFT-Based Flat Panel Design with SmartSpice

Learn About the Latest Advances in Device Modeling Using Silvaco Utmost IV

Learn How Silvaco Flow Helps Designing and Simulating Pixel Arrays in Flat Panel Displays and Detectors

How to Eliminate Image Retention Issues with SmartSpice Flex Modeling