Simulation Standard

Technical Journal

A Journal for Process and Device Engineers

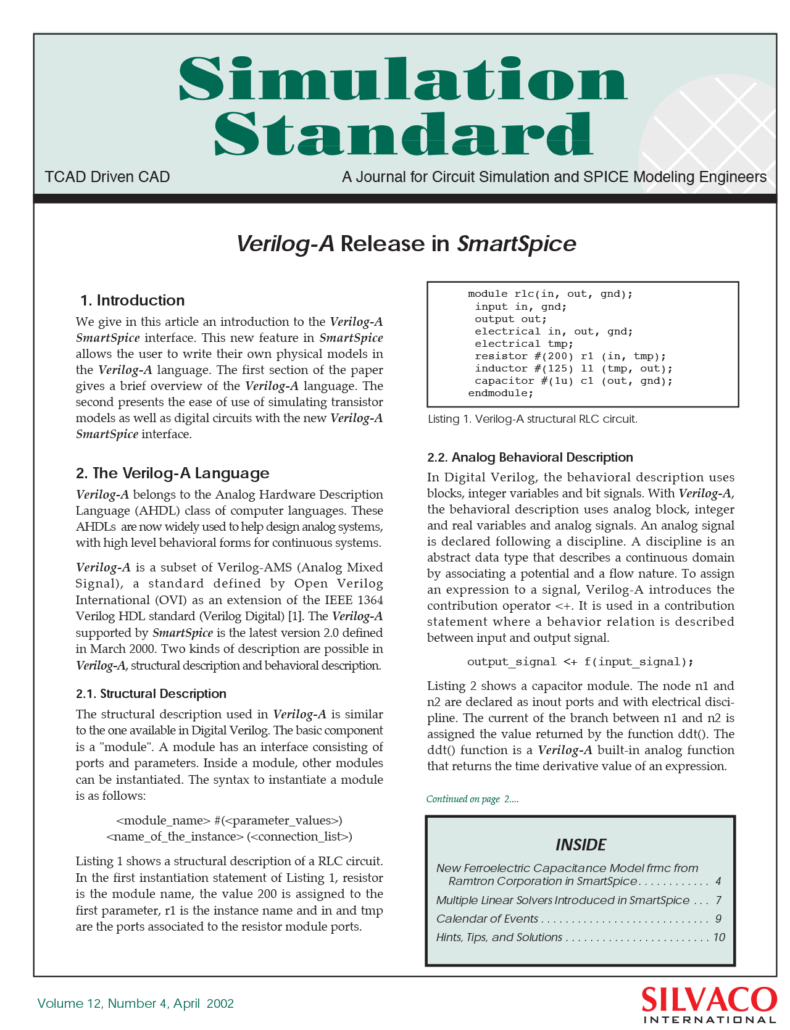

Verilog-A Release in SmartSpice

We give in this article an introduction to the Verilog-A SmartSpice interface. This new feature in SmartSpice allows the user to write their own physical models in the Verilog-A language. The first section of the paper gives a brief overview of the Verilog-A language. The second presents the ease of use of simulating transistor models as well as digital circuits with the new Verilog-A SmartSpice interface.

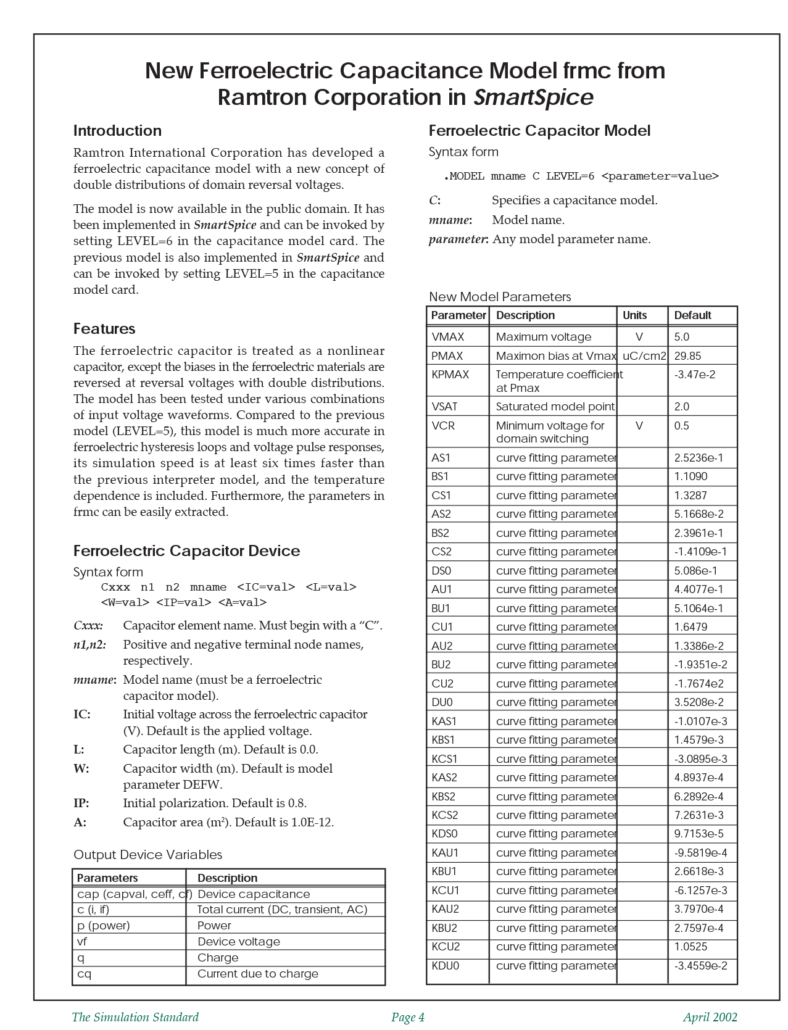

New Ferroelectric Capacitance Model frmc from Ramtron Corporation in SmartSpice

Ramtron International Corporation has developed a ferroelectric capacitance model with a new concept of double distributions of domain reversal voltages.

Multiple Linear Solvers Introduced in SmartSpice

Acknowledging the need for more flexibility, SmartSpice now provides three numerical methods for linear system solution. The additional solvers provide for greater capacity by minimizing memory requirements and reducing the overall simulation time.

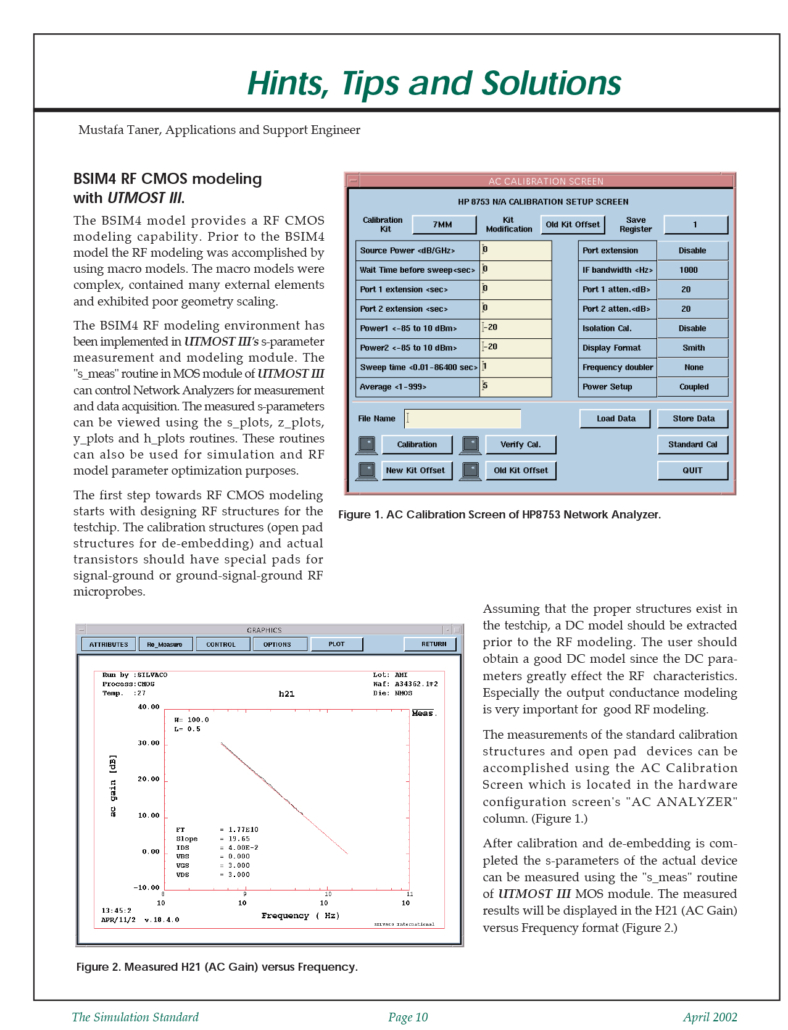

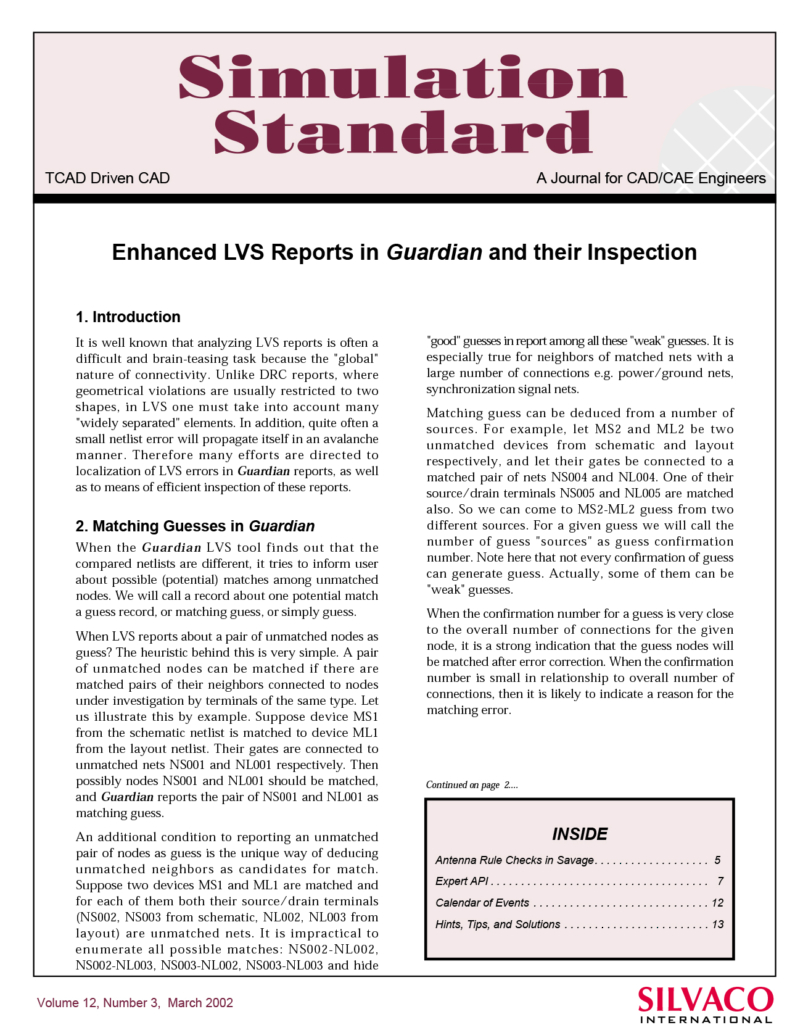

BSIM4 RF CMOS Modeling with UTMOST III

The BSIM4 model provides a RF CMOS modeling capability. Prior to the BSIM4 model the RF modeling was accomplished by using macro models. The macro models were complex, contained many external elements and exhibited poor geometry scaling.

Enhanced LVS Reports in Guardian and Their Inspection

It is well known that analyzing LVS reports is often a difficult and brain-teasing task because the "global" nature of connectivity. Unlike DRC reports, where geometrical violations are usually restricted to two shapes, in LVS one must take into account many "widely separated" elements. In addition, quite often a small netlist error will propagate itself in an avalanche manner. Therefore many efforts are directed to localization of LVS errors in Guardian reports, as well as to means of efficient inspection of these reports.

Antenna Rule Checks in Savage

Antenna rules is a common name for rules that check ratios of amounts of material in two layers from the same node. They are used to limit the damage of the thin gate oxide during the manufacturing process because of charge accumulation on interconnect layers (metal, polysilicon) on certain fabrication steps.