Applicability of Distance Computation for Graphs to LVS Discrepancy Analysis

Introduction

An important step in electronic circuit design is layout versus schematic verification (LVS). It consists of the comparison of a schematic circuit to its IC layout counterpart to determine whether they implement the same functionality. Typically, this comparison is performed in terms of spice netlists produced from the schematic and layout representation of the circuit. The ultimate goal of this verification is to ensure that these netlists completely match each other, possibly after some equivalence transformations of netlists, such as device filtering, merging, reduction. However at earlier iterations of the design cycle these netlists often fail to match. In some cases a single design error may lead to a long list of mismatched elements, and a common complaint is that LVS discrepancy reports are very difficult to analyze. Even with the aid of cross-probing and netlist browsing tools tracking the netlist discrepancies down to their source is often a tedious and time-consuming task.

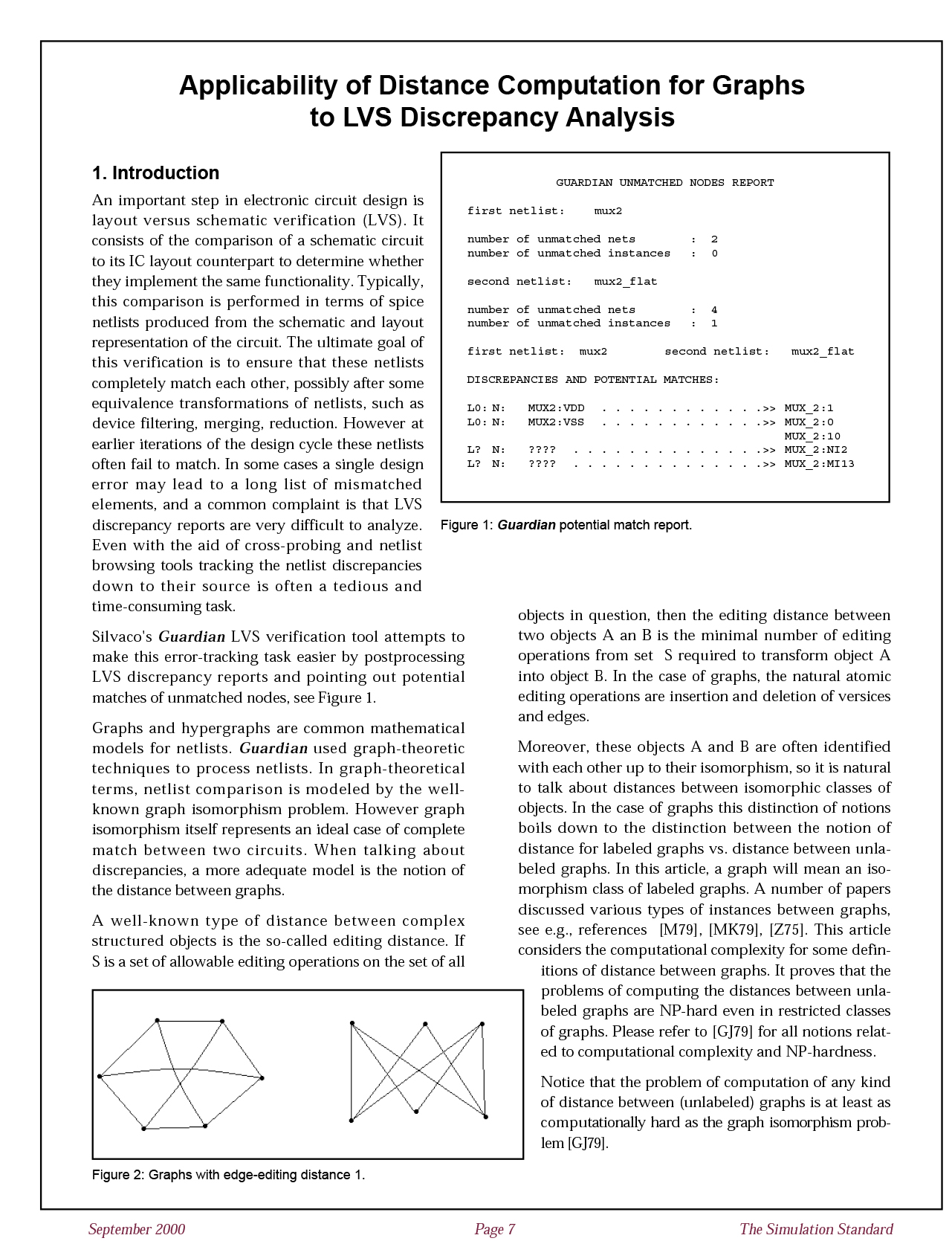

Silvaco’s Guardian LVS verification tool attempts to make this error-tracking task easier by postprocessing LVS discrepancy reports and pointing out potential matches of unmatched nodes.