Viola Cell Library Characterization and Variation Modeling

개요

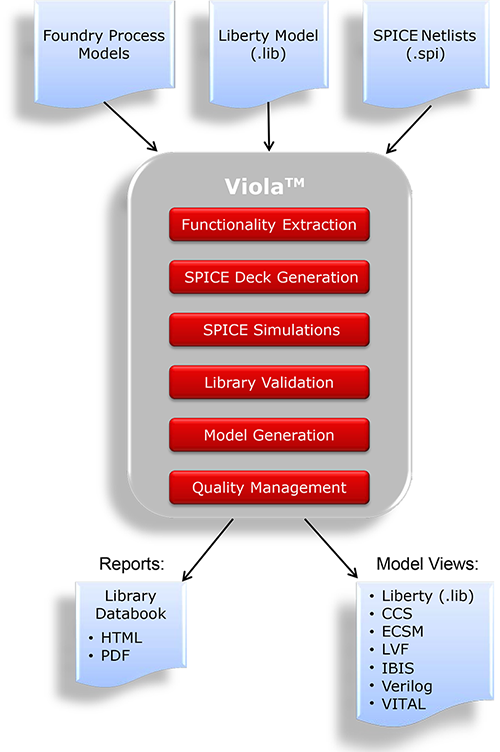

Viola는 I/O를 포함한 디지털 셀 라이브러리를 빠르고 정확하게 특성화하는 일체형 패키지입니다. 본 패키지는 stimulus를 완전히 자동으로 생성하는 실바코의 SmartSpice, 라이브러리 모델 체크 및 데이터 북 생성 기능을 포함합니다.

특성화 엔진은 필요한 stimulus 세트를 자동으로 결정하는 상세한 회로 분석을 수행하며, SPICE 데크를 생성하여, 조합 및 순차 디지털 논리 셀에 대한 모든 특성화 측정을 수행합니다.

라이브러리 품질 관리는 일련의 테스트 회로에 대해 특성화된 라이브러리를 인증하고 평가하여, SPICE 수준의 정확성과 정적 타이밍 분석과의 상관관계를 보장합니다.

특징 및 장점

- SmartSpice 시뮬레이터 및 실바코 툴 플로우와 긴밀한 통합

- HSPICE® 및 Spectre® 시뮬레이터와 완벽한 통합

- 전류원 모델링 (CCS 및 ECSM)을 통하여, 타이밍, 전력, 노이즈에 대해 향상된 특성화를 수행하여 특성화의 정확성 보장

- 성능 최적화와 함께, LVF (Liberty™ Variation Format)로 고급 공정 노드에 필요한 변동 인식 타이밍 모델 지원

- 디지털 셀의 SPICE 넷리스트로부터 자동 로직 인식

- 셀 파라미터 및 기능을 기반으로, 완전 자동화된 SPICE 데크를 생성하여 필요한 모든 논리 조합을 보장

- stimulus 및 측정을 커스터마이징하여, 복잡하고 비표준적인 셀의 특성화 지원

- 사용자가 정의한 제약 조건을 기반으로 룩업 테이블 범위 및 인덱스를 자동 결정

- 실바코의 Liberty Analyzer에서 데이터북 생성기를 완벽하게 통합하여, HTML 브라우저를 통해 손쉽게 탐색할 수 있는 계층형 데이터북 제공

- 강력한 Tcl, Perl 스크립트 환경

Library Quality Management

Library Quality Management 옵션을 사용하여, 일련의 테스트 회로에 대해 특성화된 라이브러리를 인증하고 평가하여 정적 타이밍 분석 (STA) 및 사인오프를 통해 얻어진 결과가 항상 정확하고 일관되도록 보장합니다. Viola는 추가 보정 및 특성화가 필요한 불일치에 대해 비교 보고서를 생성합니다. 본 기능은 다음의 경우에 필요합니다:

- 파운드리에서 업데이트된 트랜지스터 모델 제공

- 플로우에 신규 툴 또는 신규 버전 도입 (예. 신규 SPICE 버전, STA 툴 등)

- 상이한 타이밍 모델의 인증 및 평가 (예. NLDM vs. CCS 또는 ECSM)

- 표준 셀의 동작이 비선형적으로 될 수 있는 추가 PVT 코너에서 실행

완전성

- 비선형 지연 모델 (NLDM) 특성화 및 Current Source Model 특성화 (CCS, ECSM)를 위해 완전히 구성 가능한 2D/3D 룩업 테이블 지원

- pre-cell 드라이버 및 멀티포인트 PWL 파형으로부터 정확한 입력 파형 생성

- LSF/SGE/OGE를 통한 SPICE 시뮬레이션의 확장 가능한 병렬 실행에 필요:

- 일반적으로 사용되는 설정을 위한 직관적인 마법사 인터페이스 및 추가적인 특성화 파라미터에 필요한 광범위한 구성 옵션

- stimuli, 결과, 모델을 자체 검증

- Liberty 제약 조건 값이 입력 설정과 일치하는지 확인하기 위한 특유의 제약 조건 검증

- 코너 및 모델을 통한 일관성 검사

- 기존 Liberty 파일을 다시 특성화

- HTML 및 PDF 출력을 제공하는 유연한 데이터북 생성 기능

- 완벽한 Perl 및 Tcl 스크립트 인터페이스 지원

셀 유형

- 차동 셀과 3상 출력을 포함하는 단일, 다중 출력 조합 셀

- 순차, 조합 one-hot 셀

- 순차, 조합 멀티비트 셀

- SR-래치 및 플립플롭을 포함하는 복합적인 래치 및 플립플롭

- 상시 작동, 레벨 시프터, 전원 스위치, 유지 플립플롭 등의 저전력 셀

- 다중 전압 공급 및 경합 조건이 있는 I/O 패드

- 사용자 정의 셀

측정

- 상태 의존적 전파 지연 및 출력 전환 시간

- 최소 펄스 폭

- 설정, 유지, 복구, 제거

- 상태 의존적 내부 정적, 동적, 스위칭, 누설, 평균 전력

- 입력 핀 캐패시턴스

- CCS, ECSM 타이밍, 전력, 노이즈

- 제로 사이클 점검

입력

- PG-핀 구문을 포함한 Liberty™ 라이브러리 모델 파일

- 추출된 셀 넷리스트

- 파운드리에서 제공하는 트랜지스터 모델

출력

- CCS, ECSM 타이밍, 전력, 노이즈가 포함된 Liberty (.lib) 형식 라이브러리

- Variation-Aware 라이브러리용 LVF를 포함하는 Liberty

- I/O용 IBIS 모델

- Verilog 및 VITAL 뷰

- HTML 및 PDF 형식으로 된 라이브러리 데이터북

On-Chip 변동 및 완결 플로우: 산업적 관점

나노미터 라이브러리 특성화의 과제 및 솔루션

표준 셀 레이아웃의 마이그레이션 및 최적화