Cello Library Migration and Optimization

개요

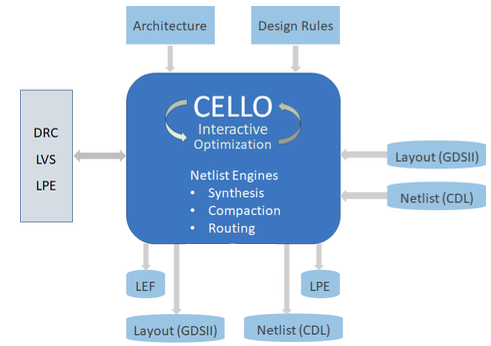

Cello는 디지털 셀 라이브러리를 이식하고 최적화하는 편리한 다용도 통합 솔루션입니다. 디지털 CMOS IC 설계에서 공정의 이식 외에, 맞춤형 디지털 셀 라이브러리를 생성하고, 대체 소자 모델, 설계 규칙, 셀 구조에 대한 영향을 분석할 수 있습니다.

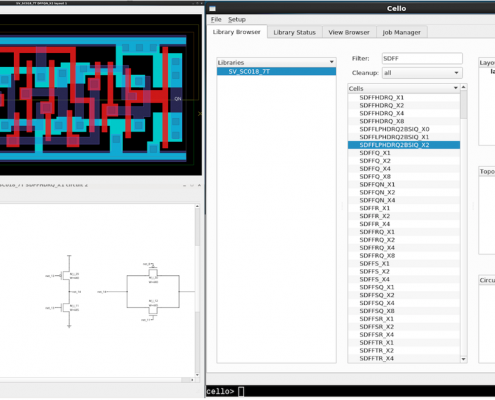

Cello를 통해, 모든 디지털 라이브러리 셀의 특성을 개별적으로 제어하고 변경할 수 있으므로 셀 파라미터를 정밀하게 조정하여 엄격한 설계 요건을 충족할 수 있습니다.

예를 들어, 트랜지스터 크기, 셀의 행 높이를 설정하여 전력 소비량, 주파수, 면적 간의 균형을 제어할 수 있습니다. 사용자는 권장되는 규칙과 필수 규칙 간에 DFM 설정을 조정하여, 전체 셀 면적의 확대 없이 레이아웃을 최적화할 수 있습니다.

Cello는 표준 셀 라이브러리의 최적화 및 마이그레이션에 필요한 툴 세트를 포함합니다. 기존 설계 플로우를 보완하여 물리적인 합성 툴 체인에 필요한 모든 출력을 제공합니다.

장점

- 레이아웃에서 수동 작업을 제거하거나 대폭 절감

- 생산성의 대폭 향상

- 핀 액세스 및 블록 접합을 포함한 구조로 수정하는 일관된 레이아웃

- 다양한 기준으로 탐색 가능 (셀 아키텍처, 설계 규칙, 크기 조정, DFM 규칙)

- 셀 아키텍처, 기술 노드 또는 파운드리 간에 레이아웃 이식

- 라이브러리 포트폴리오를 쉽게 확장

- 레이아웃 재사용

- 대화형 레이아웃 정리 및 최적화

- 구조화된 워크플로우

기능

- 공정 기술 및 파운드리 설계 규칙을 신속하게 설정하여, 사용 첫 주에 DRC 클린 레이아웃 생성 가능

- 컨텍스트에 민감한 간격 및 인클로저 규칙, 선호 형태 패턴, 자체 정렬 이중 패터닝 (SADP) 및 로컬 인터커넥트 지원 등의 고급 공정 기술

- 확장 가능한 병렬 처리로 처리량 향상

- 타사 DRC, LVS, LPE 툴과 통합하여, 사인오프 레이아웃의 품질을 보장하고 고객의 기존 플로우에 미치는 영향을 최소화

- GDSII 또는 자동으로 생성된 레이아웃으로 시작하는 호환 셀을 생성하여, 세분화된 드라이브 및 왜곡 변형을 만들고, 후반 속도 및 전력을 최적화

- Tcl 스크립트 지원으로 레이아웃 플로우에 대한 유연성 제공

- Cadence Virtuoso 플러그인

개선된 레이아웃 마이그레이션 플로우

- 셀 템플릿을 사용하여, 사전 정의된 형상, 라우팅 파라미터, 트랙 높이, 게이트 피치, P/N 비율, 전력 레일의 크기 및 위치 등을 구성

- 트랜지스터의 크기를 조정하여, 신규 템플릿 또는 드라이브 강도의 요구사항을 충족, 누설 전류가 적은 애플리케이션에 대해 게이트 길이의 변경을 허용

- GDS 기반 레이아웃 마이그레이션에 대해 방정식에 기초한 입력을 포함하여, 광범위한 레이아웃 마이그레이션 방법론 지원. 레이아웃이 특성에서 얼마나 제거되는 지에 따라, 다양한 애플리케이션 지원

- 완벽한 스크립트 인터페이스 지원으로 기존 디자인 플로우에 Cello를 통합하고, 반복 루프를 통해 설계 목표를 검색

완전성

셀 영역과 기생 효과를 최소화하는 고급 최적화 알고리즘을 사용하여 완전히 자동화된 레이아웃 토폴로지를 생성합니다. 최적화 전략에 다음 사항을 포함합니다:

- 최적의 셀 입력 시퀀싱 및 확산 스트립 레이아웃

- 내장된 트랜지스터 크기 조정 알고리즘으로 트랜지스터 넷리스트 합성 및 논리적 활동을 포함한 오버라이드 옵션

- 레이아웃 원시 요소의 파라미터 세트를 지원하는 사용자 정의 토폴로지 생성 툴:

- 컨택 및 컨택 배열

- 단일 및 접힌 트랜지스터 구성

- 라우팅 설정 및 패턴 제한/허용

- 입출력 포트 안내 및 차단

- 향상된 전용 압축 엔진:

- 적응형 토폴로지 기반 압축 전략

- 최신 CMOS 공정과 사용자 제약을 위한 전체 설계 규칙 지원

- SPICE 시뮬레이션 및 레이아웃 생성의 확장 가능한 병렬 실행에 필요:

- SUN® Grid Engine (SGE)

- 멀티 스레드 및 싱글 스레드 처리

- 내장된 검증 기능:

- 레이아웃 기능과 부울 정의의 정규 등가 점검

- 독립적인 QA를 위해 외부의 물리적 검증에 대한 인터페이스

- 외부 검증 도구를 통해 DFM 분석 및 기록

디지털 셀의 유형

- 버퍼 (inverting, non-inverting, clock)

- 부울 조합 (AND, OR, NAND, NOR, AOI, OAI, OA, AO, MUX)

- 산술 (XOR, full-adder, half-adder)

- 순차 (스캔 입력, 설정, 재설정의 최적 조합으로 래치, 클럭 게이트, D형 플립플롭)

- 기타 (타이 셀, 주입구 셀, 안테나, 다이오드, ECO 게이트)

- 부울 방정식에 기초한 사용자 정의 복합 게이트

- SPICE 넷리스트에서 사용자 정의 셀

- 전력 관리 (level-shifter, header, footer, always-on cells)

입력

- 파운드리 설계 규칙을 포함하는 실바코 테크놀로지 파일

- SPICE 넷리스트

- GDSII

출력

- LEF (Library Exchange Format)

- GDSII (Graphics Design System II) 셀 레이아웃

- 셀 스키매틱

On-Chip 변동 및 완결 플로우: 산업적 관점

나노미터 라이브러리 특성화의 과제 및 솔루션

표준 셀 레이아웃의 마이그레이션 및 최적화