Simulating Boron Diffusion in Silicon Germanium

The silicon germanium heterojunction bipolar transistor (SiGe HBT) is a promising technology for combining the operating speed of compound material devices with the production capability of bulk silicon. The presence of a narrower-bandgap material in the base region where most of the bandgap offset occurs in the valence band, creates an energy well for holes. With the lower energy barrier, a lower hole current density can be obtained for a given electron current density increasing the transistor’s gain [1]. Thus the base can then be highly doped, greatly increasing high frequency performance whilst still retaining a reasonable gain. For this reason, the diffusion of boron in SiGe is of great interest.

Simulating 3D Ohmic Heating Effects in Metal

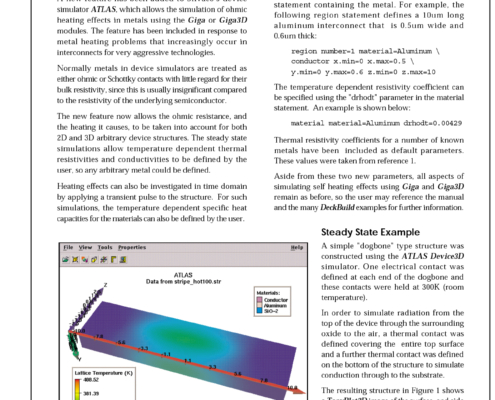

A new feature has been added to Silvaco's device simulator ATLAS, which allows the simulation of ohmic heating effects in metals using the Giga or Giga3D modules. The feature has been included in response to metal heating problems that increasingly occur in interconnects for very aggressive technologies.

The Valdinoci Temperature Dependent Impact Ionization Model for Silicon

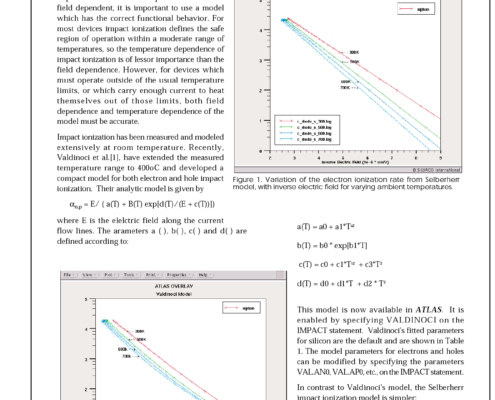

Impact ionization plays an important role in the design of many semiconductor devices. Since impact ionization is both temperature and electric field dependent, it is important to use a model which has the correct functional behavior. For most devices impact ionization defines the safe region of operation within a moderate range of temperatures, so the temperature dependence of impact ionization is of lessor importance than the field dependence. However, for devices which must operate outside of the usual temperature limits, or which carry enough current to heat themselves out of those limits, both field dependence and temperature dependence of the model must be accurate.

Reproducing Basic Experiments in ATLAS to Study the Transient Decay of Carriers

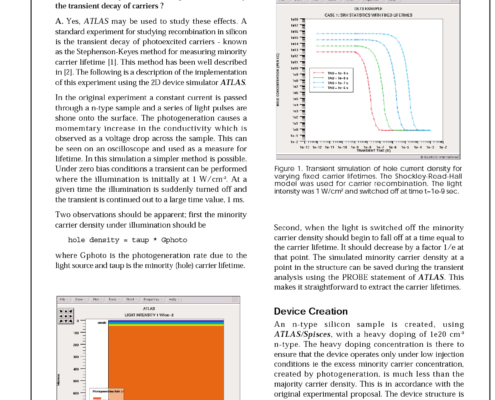

ATLAS may be used to study these effects. A standard experiment for studying recombination in silicon is the transient decay of photoexcited carriers - known as the Stephenson-Keyes method for measuring minority carrier lifetime [1]. This method has been well described in [2]. The following is a description of the implementation of this experiment using the 2D device simulator ATLAS.

BSIM3SOI Version 3.0 Model Released in SmartSpice

BSIM3SOI version 3.0 model was released on May 2002 by UC Berkeley. This model includes both Partially and Fully depleted models. This model is now implemented in SmartSpice and can be selected according to LEVEL selector.

A New Surface-Potentials Based MOSFET Model: HiSIM

HiSIM is based on a charge-sheet model. IDS current is described using only one equation, and there-fore is continuous over the whole range of operating regions. This improves MOSFETs modeling regarding at least two points. Equations are continuous over all operation regions, as well as their derivatives. This is a key point for today’s analog circuits, where performance is very much dependent on high order derivatives. Parameter number is dramatically reduced (by a factor 5) for the same level of accuracy. Parameters are not interdependent anymore, making extraction easier. Furthermore, a set of parameters is valid for all channel lengths.

HiSIM Version 1.0 Model Released in UTMOST III

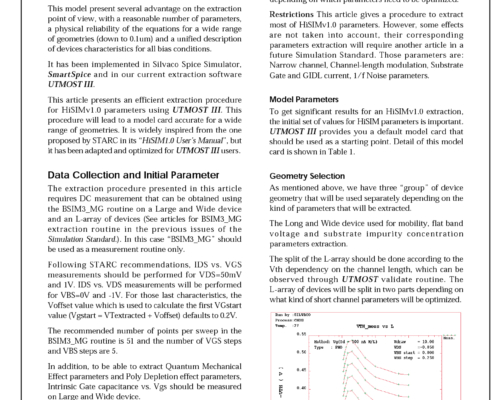

HiSIM is a MOSFET model for SPICE circuit simulation that has been developed by Hiroshima University and STARC Company. This model present several advantage on the extraction point of view, with a reasonable number of parameters, a physical reliability of the equations for a wide range of geometries (down to 0.1um) and a unified description of devices characteristics for all bias conditions. It has been implemented in Silvaco Spice Simulator, SmartSpice and in our current extraction software UTMOST III.

Measure Low Current FT in Bipolar devices

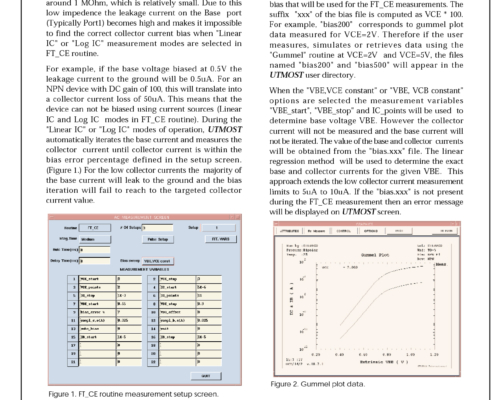

The input impedence of most network analyzers are around 1 MOhm, which is relatively small. Due to this low impedence the leakage current on the Base port (Typically Port1) becames high and makes it impossible to find the correct collector current bias when "Linear IC" or "Log IC" measurement modes are selected in FT_CE routine.

Parallel DRC by Functional Decomposition of DRC Decks

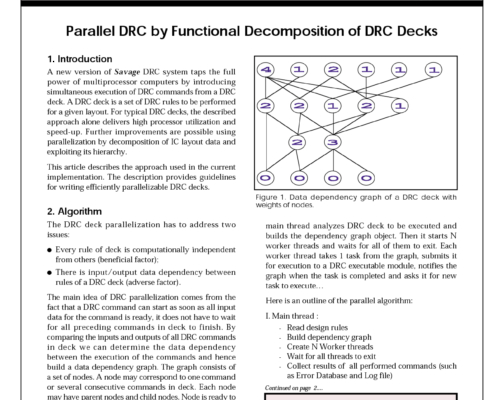

A new version of Savage DRC system taps the full power of multiprocessor computers by introducing simultaneous execution of DRC commands from a DRC deck. A DRC deck is a set of DRC rules to be performed for a given layout. For typical DRC decks, the described approach alone delivers high processor utilization and speed-up. Further improvements are possible using parallelization by decomposition of IC layout data and exploiting its hierarchy.

Expert Layout Editor, Savage DRC System and Guardian LVS for Linux Platform

Silvaco Data Systems announces the release of CELEBRITY CAD suite: Expert layout editor, Savage DRC system and Guardian LVS for Linux platform.