Guardian LVS: New Platform-Independent GUI

We introduce a platform-independent version of Guardian LVS. An important feature of any tool is its capability to operate on various platforms and to support internationalization. Now Guardian LVS is a multiplatform application operating on the following platforms: Windows, Linux and Solaris (32- and 64-bit versions).

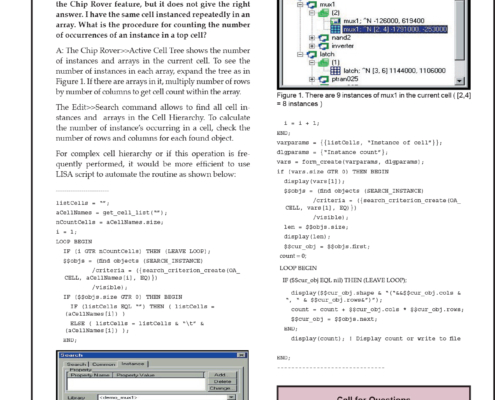

Counting Instances in an Expert Editor Layout

Q: I have some trouble counting the number of in-stances in a layout using Expert. I have tried to use the Chip Rover feature

Low Voltage Super Junction MOSFET Simulation and Experimentation

The application of Super Junction concepts to a low voltage power MOSFET is investigated. The body junction is modified with the addition of a high energy implant, resulting in an increased breakdown voltage. Simulations are used to quantify the relationship between dose and breakdown voltage, resulting in a predicted 35% Rds(on) reduction. This is confirmed through experiment, and a 19% reduction in Rds(on) is reported at 75 V. No change in device reliability is observed. This approach provides a simple means to reduce the on resistance of low voltage MOSFETs.

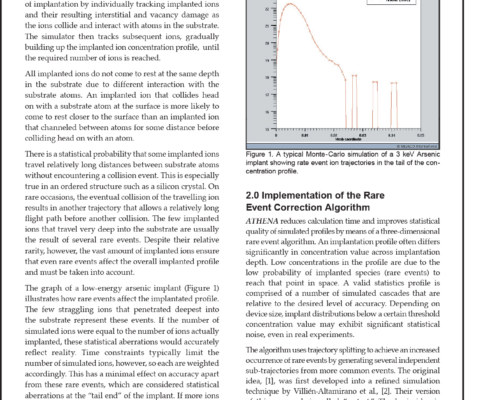

Using The Statistical Sampling Feature in the BCA Monte Carlo Implant Simulator

Silvaco’s Binary Collision Approximation (BCA) Monte- Carlo Implantation simulator closely replicates the physics of implantation by individually tracking implanted ions and their resulting interstitial and vacancy damage as the ions collide and interact with atoms in the substrate. The simulator then tracks subsequent ions, gradually building up the implanted ion concentration profile, until the required number of ions is reached.

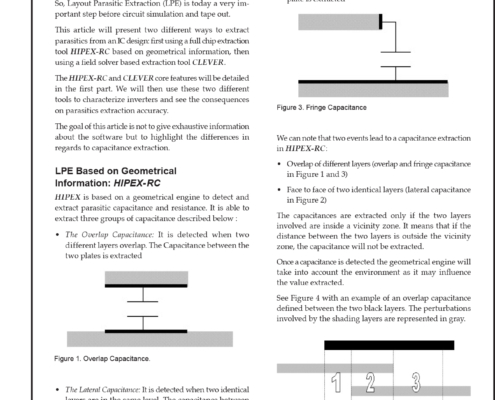

A Comparison Between Classical Full Chip Extraction and Field Solver Parasitic Extraction

This article will present two different ways to extract parasitics from an IC design: first using a full chip extraction tool HIPEX-RC based on geometrical information, then using a field solver based extraction tool CLEVER.

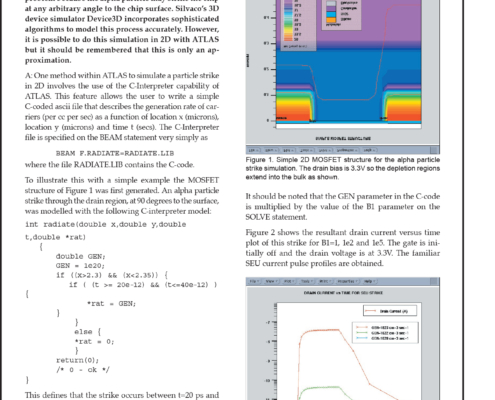

ATLAS Simulation of an SEU Event in 2D

Q: Can ATLAS simulate an SEU event in 2D? To simulate a single event upset (SEU) is inherently a 3D problem because the alpha particle may strike the chip at any arbitrary angle to the chip surface. Silvaco’s 3D device simulator Device3D incorporates sophisticated algorithms to model this process accurately. However, it is possible to do this simulation in 2D with ATLAS but it should be remembered that this is only an approximation.

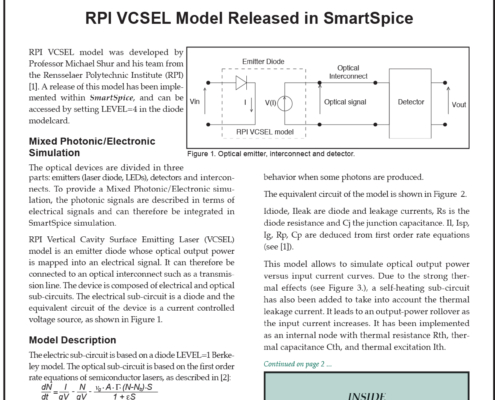

RPI VCSEL Model Released in SmartSpice

RPI VCSEL model was developed by Professor Michael Shur and his team from the Rensselaer Polytechnic Institute (RPI) [1]. A release of this model has been implemented within SmartSpice, and can be accessed by setting LEVEL=4 in the diode modelcard.

BSIM3v3 Model Verilog-A Implementation

Berkeley University BSIM3v3 model is the industry-standard, physics-based, deep-submicron MOSFET model for digital and analog circuit designs. This makes BSIM3v3 model a good candidate for implementation in Verilog-A HDL for study purpose or customized model use.

New Device Model Card Approach

Normally a single active device model is extracted to cover a range of device geometries and temperature. Sometimes this single scalable model is not sufficient to describe all the changes in output characteristics over the range of geometry and temperature required. The total range of geometry and temperature is then broken up into regions and a model produced for each of these sub-sets of devices. This is the basis of a binned model and can lead to discontinuities at the bin boundaries as the model card is changed. To get round this problem SmartSpice has introduced a new functionality to allow the user to go back towards a single scalable model card via the use of a function rather than a single parameter value.

SmartSpice Tips: Memory Usage, .MODIF & .ALTER, Non-convergence

When you run a long simulation time analysis the evaluated time points are normally all held in memory until the end time is reached. All the data is then written out to the output rawfile. This means a large amount of system memory can be used up and also has to be tracked. If in the input deck the line “.OPTIONS RAWPTS=300 POST” is included then as soon as the maximum number of points is reached given by “RAWPTS=300” then all the vector data is saved to the raw data output file and the memory is free to be re-used. In this way the output rawfile is incrementally increased in size every time this limit is reached. The memory required by the simulation run is therefore reduced, and with less memory to manage, the simulation is run faster. This is particularly useful on the PC platform where some of the memory is required for the operating system and RAM size is less than 1GB.