Viola セル・ライブラリ・キャラクタライゼーション/バリエーション(ばらつき)・モデリング

概要

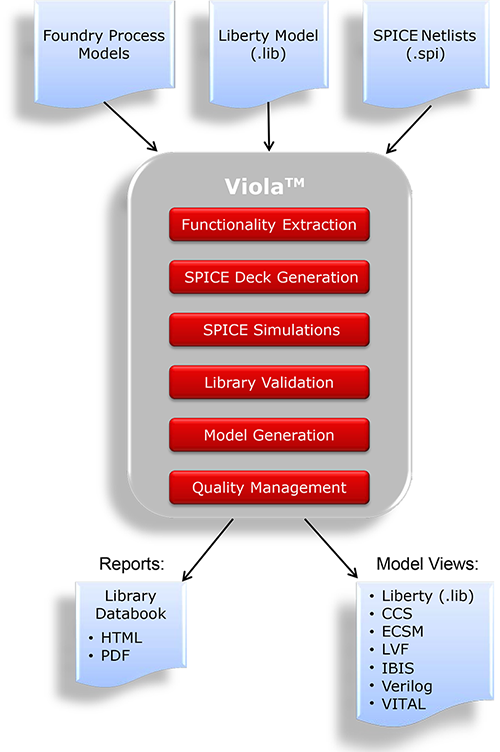

Violaは、I/Oを含むデジタル・セル・ライブラリのキャラクタライズを迅速かつ正確に行うための、ユニークな総合パッケージです。このパッケージには、完全に自動化されたスティミュラス生成機能を持つシルバコSmartSpice、ライブラリ・モデル・チェッカ、データブック・ジェネレータが含まれています。

キャラクタライズ・エンジンは、詳細なセル回路解析を行い、必要なスティミュラスのセットを自動的に決定し、組み合わせ型およびシーケンシャル型のデジタル・ロジック・セルのすべてのキャラクタライズ測定を行うためのSPICEデッキを作成します。

また、ライブラリの品質管理により、キャラクタライズされたライブラリを一連のテスト回路で検証・評価し、SPICEレベルの精度とスタティック・タイミング解析との相関性を確保します。

特長と利点

- シミュレータSmartSpiceとシルバコ・ツール・フローとの密接な統合

- HSPICE®およびSpectre®シミュレータとの統合

- 電流源モデリング(CCSおよびECSM)によるタイミング、パワー、ノイズの高度なキャラクタライズにより、キャラクタライズの精度を確保

- パフォーマンスを最適化したLiberty™ Variation Format (LVF)による先進的なプロセス・ノードのばらつきを考慮したタイミング・モデルをサポート

- デジタル・セルのSPICEネットリストから論理を自動認識

- セルのパラメータと機能の両方に基づいて完全に自動化され生成されたSPICEデッキは、必要な論理の組み合わせをすべてカバー

- 複雑で非標準的なセルのキャラクタライズをサポートするためのスティミュラスおよび測定のカスタマイズ

- ユーザ定義の制約に基づくルック・アップ・テーブルの範囲とインデックスの自動決定

- シルバコの Liberty Analyzerのデータブック・ジェネレータとの完全な統合により、HTMLブラウザで簡単にナビゲーションできる階層化されたデータブックを提供

- 強力なTclおよびPerlスクリプト環境

ライブラリの品質管理

Library Quality Managementオプションでは、キャラクタライズされたライブラリを一連のテスト回路で評価し、静的タイミング解析(STA)からサインオフに至るまで、正確で一貫した結果が得られるよう保証します。Violaは比較レポートを作成し、さらなるキャリブレーションとキャラクタライズが必要となるような不一致をハイライトします。 この機能は次のような場合に必要です。

- ファウンドリが最新のトランジスタ・モデルを提供

- フローに新しいツールやツールのバージョンを導入する(例:SPICEの新バージョン、STAツールなど)

- 異なるタイミング・モデルの認定や評価(例:NLDMとCCSやECSMの比較)

- PVTコーナを追加して実行した際の、標準的なセルの挙動が著しく非線形になるような場合

完全性

- 非線形遅延モデルの特性評価(NLDM)および電流源モデルの特性評価(CCSおよびECSM)のための、完全に設定可能な2次元および3次元のルック・アップ・テーブルをサポート

- プリセル・ドライバおよびマルチポイントPWL波形からの正確な入力波形生成

- LSF/SGE/OGEによるSPICEシミュレーションのスケーラブルな並列実行

- 一般的な設定のための直感的なウィザード・インターフェースと、追加の特性パラメータのための広範囲かつ高度な設定オプション

- スティミュラス、結果、モデルを組み込み検証

- リバティの制約値が入力設定と一致するかどうかを検証する独自の制約検証機能

- コーナとモデルの整合性チェック

- 既存のLibertyファイルの再キャラクタライズ

- HTMLおよびPDF出力を提供する柔軟なデータブック・ジェネレータ

- PerlとTclのスクリプト・インタフェイスをサポート

セル・タイプ

- 差動セルやトライステート出力を含むシングルおよびマルチ出力の組み合わせセル

- 逐次型および組合せ型ワンショット・セル

- 逐次型および組合せ型マルチビット・セル

- SR-ラッチやSR-フリップフロップを含む複雑なラッチやフリップフロップ

- 常時オン、レベルシフタ、パワー・スイッチ、保持型フリップフロップなどの低消費電力セル

- 複数の電圧供給と競合条件を持つI/Oパッド

- カスタム・セル

測定

- 状態に依存する伝搬遅延時間と出力遷移時間

- 最小パルス幅

- セットアップ、ホールド、リカバリ、およびリムーバル

- 状態に依存する内部のスタティック、ダイナミック、スイッチング、リーク、および平均電力

- 入力端子の静電容量

- CCSおよびECSMのタイミング、電力、ノイズ

- ゼロ・サイクル・チェック

入力

- Liberty™ライブラリのモデルファイル(PG-pinシンタックスを含む)

- 抽出されたセル・ネットリスト

- ファウンドリが提供するトランジスタ・モデル

出力

- CCSおよびECSMのタイミング、パワー、ノイズを含むLibertyフォーマットのライブラリ

- ばらつきを考慮したライブラリのLVFを含むLibertyファイル

- I/OのIBISモデル

- VerilogおよびVITALビュー

- HTMLとPDF形式のライブラリ・データブック

リソース不足を上手に解決!シルバコの提供する3つの開発サービス

オンチップばらつきおよびサインオフ・タイミング・フロー: 業界の視点

ナノメータ・プロセスにおけるスタンダード・セル・ライブラリのキャラクタライゼーション:課題とソリューション

スタンダード・セル・レイアウトのマイグレーションと最適化