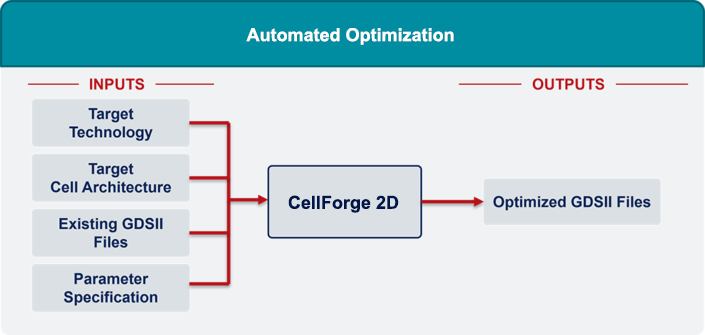

Automated Optimization

Overview

CellForge 2DTM centralizes and automates the design of digital standard cell libraries within a single solution. It provides designers with the ability to control and modify the individual attributes of all cells in a library, allowing for precise adjustments to meet even the strictest design requirements. CellForge 2D enables engineers to reuse existing work to fine-tune transistor sizing, row height, design for manufacturability rules (DFM), and other design parameters to manage the trade-offs between power consumption, frequency, and area. Additionally, CellForge 2D offers a comprehensive layout customization scripting interface using TCL, integration with third-party verification tools (DRC, LVS, and PEX) with minimal disruption, and flexibility to use within a layout editing flow.

Advanced Layout Automation Flow

- Compatible with all design rules

- Supports both single and double-height cells

CellForge 2D Flow

Key Features

- Fast setup of process technologies and foundry design rules, enabling DRC clean layout generation in the first week of use

- Advanced process technology, including context sensitive spacing and enclosure rules, preferred shape patterns, self-aligned double patterning (SADP) and support of local interconnect

- Scalable parallel processing to improve throughput

- Integration with leading third-party DRC, LVS and LPE tools to ensure high-quality sign-off layouts and minimal disruption to customer existing flows

- Generate footprint-compatible cells starting with GDSII or automatically generated layouts to create fine-grained drive and skew variants, enabling late-stage speed and power optimization

- TCL scripting support provides the flexibility to customize the layout flow.

- Cadence Virtuoso plugin

Key Benefits

- Eliminate or significantly reduce layout manual effort

- Significantly improve productivity

- Enables exploration of different dimensions (cell architecture, design rules, sizing strategy, DFM rules)

- Migrate layouts between cell architectures, technology nodes or foundries

- Easily expand your portfolio of libraries

- Reuse layouts

- Interactive layout cleanup and optimization

- Structured workflow: 2-week ramp-up for new Layout Engineers