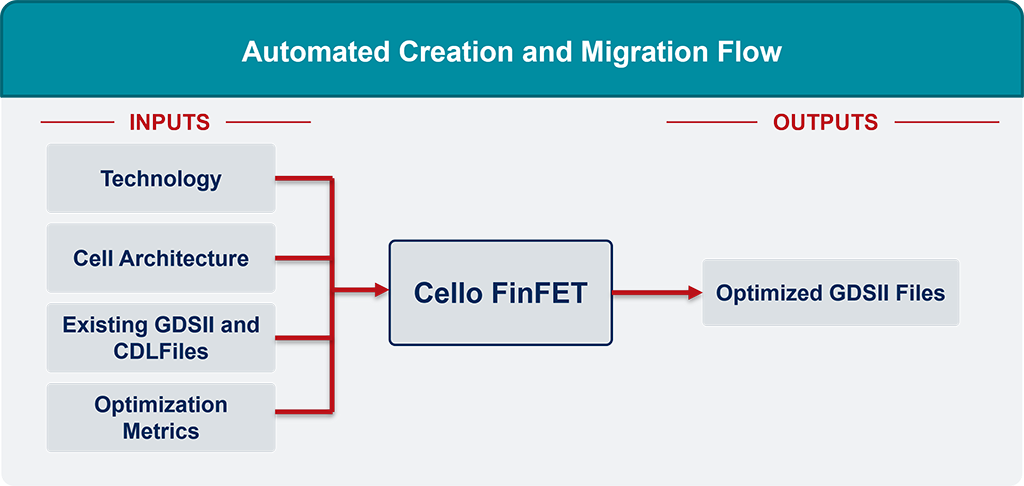

Cello FinFET Flow

Key Features

- Sub-10nm FinFET support

- Integrated place and route engine creates correct by construction layout

- Compatible with multi-patterning rules, cut rules, or any other complex FinFET processes rules

- Advanced process technology, including context sensitive spacing and enclosure rules, preferred shape patterns, self-aligned double patterning (SADP) and support of local interconnect

- Scalable parallel processing to improve throughput

- Multiple layout options are created simultaneously

- Integration with leading third-party DRC, LVS and LPE tools to ensure high-quality sign-off layouts and minimal disruption to existing flows

- Flexible setup of process technologies and foundry design rules, enabling ultra-fast, DRC clean layout generation

Key Benefits

- Significantly improves productivity

- Eliminates or greatly reduces manual layout effort

- Fast turnaround time, complete library in one day

- Enables exploration of different dimensions (cell architecture, design rules, sizing strategy, different track heights, DFM rules)

- Consistent layout

- Reuse of schematics reduces design time

- Automates PDK updates

リソース不足を上手に解決!シルバコの提供する3つの開発サービス

オンチップばらつきおよびサインオフ・タイミング・フロー: 業界の視点

ナノメータ・プロセスにおけるスタンダード・セル・ライブラリのキャラクタライゼーション:課題とソリューション

スタンダード・セル・レイアウトのマイグレーションと最適化