/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Graham Bell

/wp-content/uploads/2019/11/silvaco-logo.png

Graham Bell2020-04-07 00:24:212024-05-02 13:22:09Silvaco Licenses HiSIM_IGBT Power Device Model Developed by HiSIM Consortium and Provides Support in SmartSpice Circuit Simulator

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Graham Bell

/wp-content/uploads/2019/11/silvaco-logo.png

Graham Bell2020-04-07 00:24:212024-05-02 13:22:09Silvaco Licenses HiSIM_IGBT Power Device Model Developed by HiSIM Consortium and Provides Support in SmartSpice Circuit Simulator

Utmost IV Quick-Start Model Optimization Templates

本ウェビナーでは、Utmost IV Quick-Start Optimization Templatesの新機能をご紹介します。

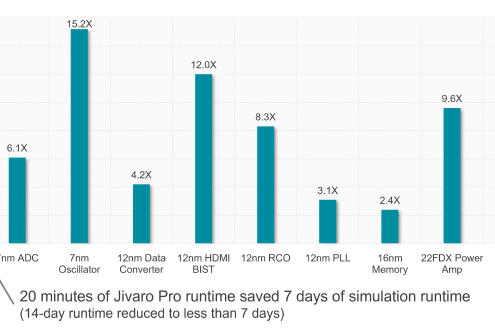

Jivaro寄生リダクションによる回路シミュレーションの加速

Jivaroを簡単に紹介した後、シミュレーション・フローを向上する手法を示し、高度なネットリスト・リダクションを行うために必要な機能および制御を確認します。

寄生素子リダクション

Jivaro Proは、寄生素子ネットワークの削減によるシミュレーション時間の短縮に特化した独自のスタンドアローンソリューションです。Jivaro Proの高いリダクション率は、シミュレーション時間を数日から数時間にまで劇的に短縮することが証明されています。

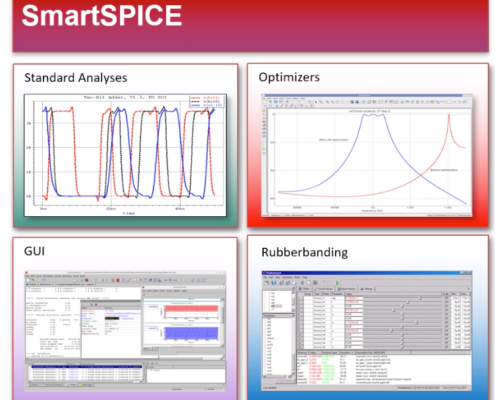

回路ラバーバンド

SmartSpiceとGatewayのラバーバンド機能を使えば、アナログ設計の改善が容易になります。モデルやデバイスのインスタンス・パラメータの値を任意の組み合わせで変更すると、ラバーバンド機能によって回路性能の変化がリアルタイムにフィードバックされます。

回路シミュレータ

シルバコのSmartSpice™は、業界をリードする精度を誇る高性能パラレルSPICEシミュレータです。複雑な高精度アナログおよびミックスドシグナル回路のシミュレーション、メモリ、カスタム・デジタル設計、先端半導体プロセスのセル・ライブラリの特性評価などのアプリケーションに対応する、実績のある包括的なソリューションです。

ばらつきおよび歩留まり解析

VarManの革新的な技術は、高度な機械学習アプローチを用いて、精度と正確さを維持しながら、従来のモンテカルロシミュレーションと比較して最大30倍のシミュレーション性能を実現します。ハイシグマが要求される設計において、VarManは、設計チームが精度を重視した解析を容易に実現できるようにします。VarManは、キャラクタライズ・プロジェクトのセットアップを簡素化するように設計されており、設計者がセットアップと実行を行う手間がかかりません。フルチップのXMAメモリの歩留まり解析では、VarManの革新的な高速モンテカルロとロバストなハイシグマ・カーネルを使用して、メモリ全体の高速なフェイル検出と歩留まり推定を行います。

アナログ・シミュレーション

シルバコのSmartSpiceは、業界をリードする精度を実現する高性能なパラレルSPICEシミュレータです。複雑な高精度アナログ/ミックスドシグナル回路のシミュレーション、メモリ、カスタム・デジタル設計、先端半導体プロセスのセル・ライブラリの特性評価などのアプリケーションに対応した、実績のある包括的なソリューションです。複数のソルバー、ステッピング・アルゴリズム、計算技術を導入したインテリジェントなアーキテクチャを採用しています。

寄生素子リダクションおよび解析

シルバコの寄生ネットリスト解析ツールおよびリダクション・ツールでは、パフォーマンス、速度、精度すべてを兼ね備えています。シルバコは、アナログ、デジタル、RF、ミックスドシグナル、メモリ・デザインのポスト・レイアウト検証フロー全体をスピードアップさせる包括的な解析ツールを提供します。

SPICEモデル作成

シルバコのUtmost IVは、最先端のCMOSおよび化合物半導体デバイスの特性評価とモデリングにおけるこれらの課題を解決する業界随一のソリューションです。