Inductance Optimization using 3D Field Solver based on Design Of Experiment Approach

Abstract

A new 3D electromagnetic simulator coupled with a statistical analysis, for inductance loop optimization is presented. It allows RF designers to easily create inductor design by only specifying as inputs the desired inductance and Q factor for example and get as outputs layout parameters like radius, wire width, space between wires and numbers of coils. To do so, inductance simulations using Design of Experiments (DoE) approach are done and subsequent Response Surface Model (RSM) are generated. Performing an optimization on the RSM model a gds2 inductance loop layout is generated according to the user specified initial constraints and will be ready to use in a design of RF-circuits. Inherent to this new methodology the designers can now take into account process variations which is mandatory for current technology node.

1. Introduction

Up to a few Ghz, on-chip inductors are among the most critical components to design radio-frequency integrated circuits (RFIC). The main parameters that characterize an inductor are its self-inductance value L, its cut-off frequency and its quality factor Q (a good inductor has a high Q). For on-chip inductors, Q is limited for example by the inductor’s series resistance, the resistive loss (skin effect and proximity effect) and the current induced by the capacitive coupling to the ground plane and the substrate. In this context it is imperative to allow engineers to easily and accurately create any RF structure and give designers the flexibility to innovate new geometries simply by editing parameters such as radius, number of turns, width and spacing of coils. The aim of this paper is indeed to explain how this can be possible using a specific methodology based on Design Of Experiments approach in combination with a new field solver simulator.

2. 3D Electromagnetic Simulation

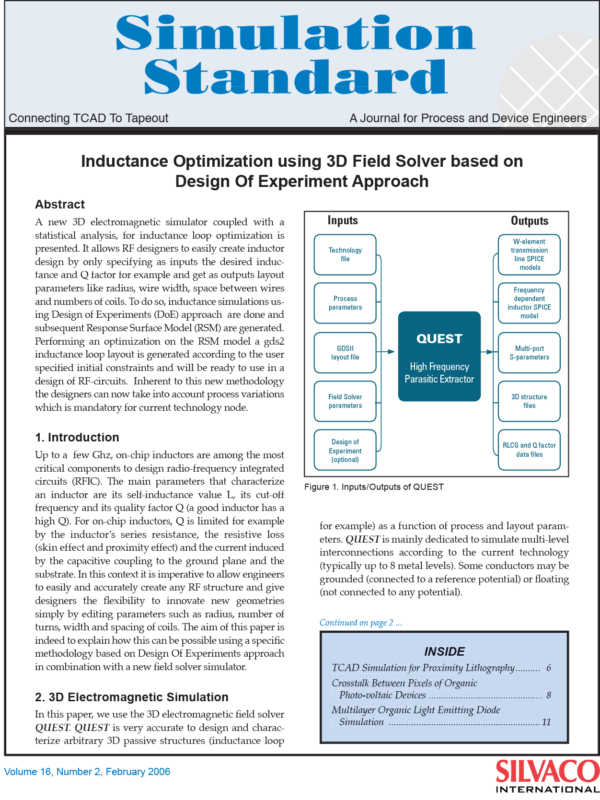

In this paper, we use the 3D electromagnetic field solver QUEST. QUEST is very accurate to design and characterize arbitrary 3D passive structures (inductance loop for example) as a function of process and layout parameters. QUEST is mainly dedicated to simulate multi-level interconnections according to the current technology (typically up to 8 metal levels). Some conductors may be grounded (connected to a reference potential) or floating (not connected to any potential).

QUEST computes firstly the 3D structure resulting of the layout information, process and techno file inputs, then, after simulation, Quest can give RLGC parameters, S-Y-Z-parameters, Q factor and spice model for inductance loop simulation and standard Spice W-element format for transmission line simulation (Figure 1). All these output parameters are function of the frequency. These results are stored in a database and can be used in post-treatment for statistical analysis for example.