Simulate 40X Faster with SmartSpice HPP

In this webinar, we describe how SmartSpice HPP takes advantage of the modern multicore hardware platforms to speed up all internal aspects of transient simulations of analog circuits by adopting a partition-based simulation.

Using SmartSpice Compact Models

June 11, 2020 | 10:00 am – 10:30 am (PDT)

This webinar will provide a guide to developing Compact Models in SmartSpice to achieve optimal simulation performance. You will learn how models are used in SmartSpice and best practices when constructing a custom Verilog-A model.

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Graham Bell

/wp-content/uploads/2019/11/silvaco-logo.png

Graham Bell2020-04-07 00:24:212024-05-02 11:47:14Silvaco Licenses HiSIM_IGBT Power Device Model Developed by HiSIM Consortium and Provides Support in SmartSpice Circuit Simulator

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Graham Bell

/wp-content/uploads/2019/11/silvaco-logo.png

Graham Bell2020-04-07 00:24:212024-05-02 11:47:14Silvaco Licenses HiSIM_IGBT Power Device Model Developed by HiSIM Consortium and Provides Support in SmartSpice Circuit Simulator /wp-content/uploads/2019/11/silvaco-logo.png

0

0

Ingrid Schwarz

/wp-content/uploads/2019/11/silvaco-logo.png

Ingrid Schwarz2020-01-16 19:31:102021-04-23 13:16:08Accelerate the Circuit Simulation Flow with Jivaro Parasitic Reduction

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Ingrid Schwarz

/wp-content/uploads/2019/11/silvaco-logo.png

Ingrid Schwarz2020-01-16 19:31:102021-04-23 13:16:08Accelerate the Circuit Simulation Flow with Jivaro Parasitic Reduction

Parasitic Reduction

Jivaro Parasitic Reduction for Fast, Accurate Simulation

Jivaro is a unique stand-alone solution dedicated to the reduction of parasitic networks. It helps back-end verification teams speed up post-layout SPICE simulation of huge extracted parasitic circuits, while keeping high accuracy.

Circuit Simulation

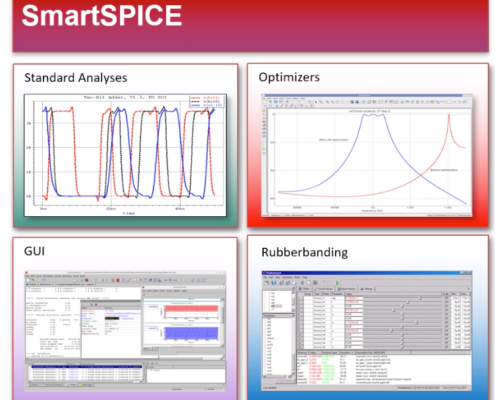

SmartSpice Circuit Simulator

Silvaco’s SmartSpice™ is a high performance parallel SPICE simulator that delivers industry leading accuracy. It is a proven, comprehensive solution for applications including simulation of complex high precision analog and mixed-signal circuits, memory, custom digital design and characterizing cell libraries of advanced semiconductor processes.

Circuit Rubberband

Real-time Circuit Simulation Rubberband Capability

With the rubberband feature of SmartSpice and Gateway analog design improvement is made easy. Changing values of models or device instance parameters in any combination provides realtime feedback on the change in circuit performance through the rubberband capability.

Analog Simulation

Silvaco’s SmartSpice is a high performance parallel SPICE simulator that delivers industry leading accuracy. It is a proven, comprehensive solution for applications including simulation of complex high precision analog and mixed-signal circuits, memory, custom digital design and characterizing cell libraries of advanced semiconductor processes. It uses an intelligent architecture deploying multiple solvers, stepping algorithms and computation techniques. The result is accurate, robust convergence and industry leading performance and capacity – over 8 million active devices. It is compatible with HSPICE® and Spectre® for netlists, models, analysis features, and results – plus large libraries of calibrated device models are available. Featuring integration with Silvaco Gateway schematic editor and SmartView waveform viewer, SmartSpice fits seamlessly into front-end analog IC design flows.

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Ingrid Schwarz

/wp-content/uploads/2019/11/silvaco-logo.png

Ingrid Schwarz2019-09-16 00:00:002020-12-20 19:07:41Silvaco Partners with HDL Design House for Analog and Digital IC Design Services

/wp-content/uploads/2019/11/silvaco-logo.png

0

0

Ingrid Schwarz

/wp-content/uploads/2019/11/silvaco-logo.png

Ingrid Schwarz2019-09-16 00:00:002020-12-20 19:07:41Silvaco Partners with HDL Design House for Analog and Digital IC Design Services